1、 概述

AD9751是一个双输入端口的超高速10位CMOS DAC。它内含一个高性能的10位D/A内核、一个基准电压和一个数字接口电路。当AD9751工作于300MSPS时,仍可保持优异的交流和直流特性。

AD9751 的数字接口包括两个缓冲锁存器以及控制逻辑。当输入时钟占空比不为50%时,可以使用内部频率锁相环电路(PLL)。此时,频率锁相环电路将以两倍于外部应用时钟的速度来驱动DAC锁存器,并可从两个输入数据通道上交替传输数据信号。其输出传输数据率是单个输入通道数据率的两倍。当输入时钟的占空比为 50%或者对于时钟抖动较为敏感时,该锁相环可能失效,此时芯片内的时钟倍增器将启动。因而当锁相环失效时,可使用时钟倍增器,或者在外部提供2倍时钟并在内部进行2分频。

CLK输入端(CLK+CLK-)能以差分方式或者单端方式驱动,这时信号压摆率可低至1V的峰峰值。由于AD9751采用分段电流源结构,因而可运用适当的开关技术去减小干扰,以使动态精度达到最了。其差分电源输出可支持单端或差分应用。每个差分输出端均可提供从2mA~20mA的标称满量程电流。

AD9751采用选进的低成本的0.35μm的CMOS工艺制造。它能在单电源2.7V~3.6V下工作,其功耗小于300mW。

AD9751具有如下主要特点:

为高速TxDAC+s系列成员之一,且与该系列其它芯片的引脚兼容,可提供10、12和14位的分辨率。 具有超高速的300MSPS转换速率。 带有双10位锁存和多路复用输入端口。 内含时钟倍增器,可采用差分和单端时钟输入。 功耗低,在2.7V~3.6V的单电源时,其功率低于300mW。片内带有1.20V且具有温度补偿的带隙电压基准。

2、AD9751的引脚功能

AD9751采用48脚LQFP封装,其工作温度范围为-40~+85℃,各主要引脚的功能如下:

IOUTA(43脚):差分DAC电流输出端; IOUTB(42脚):差分DAC电流输出端; REFIO(39脚):基准输入/输出端; DIV0,DIV1(37,38脚):PLL控制和输入端口模式选择输入脚; FSADJ(40脚):满刻度电流输出调节端; AVDD(41脚):模拟电源电压; ACOM(44脚):模拟公共端; DVDD(5,21脚):数字电源电压; DCOM(4,22脚):数字公共端; PLLVDD(47脚):相位锁存回路电源电压; CLKVDD(48脚):时钟电源电压; CLKCOM(45脚):时钟和相位锁存回路公共端; CLK+(2脚):差分时钟输入端; CLK-(3脚):差分时钟输入端; LPF(46脚):PLL的低通滤波器; RESET(1脚):内部时钟分频器清零; PLL-LOCK(6脚):PLL锁定显示器输出; DB8-P1/DB0-P1(7~16脚):数据位,DB9~DB0,端口1; DB9-P2/DB0-P2(23~32脚):数据位,DB9~DB0,端口2。

3 、工作原理

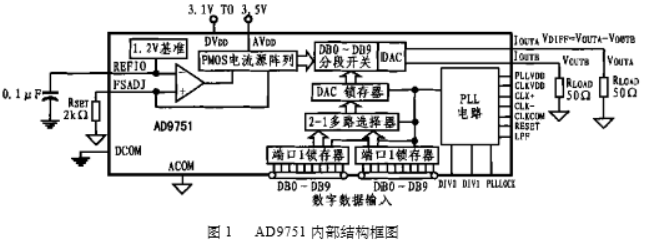

图1 是AD9751的内部原理结构和外围设计电路简化方框图。可以看出:AD9751包括一个能提供高达20mA满量程电流(IOUTFS)的PMOS电流源阵列。该阵列被分成31个相等电流源并由它们组成5个最大有效位(MSB)。接下的4位,或中间位,由15个相等的电流源组成,它们的值为一个最大有效位电流源的1/16,剩下的LSB是中间位电流源的二进制权值的一部分。AD9751采用电流源实现中间位和较低位,而不是用R-2R梯形网络,因而提高了多量程时小信号的动态性能,并且有助于维持DAC的高输出阻抗特性(例如100kΩ)。

AD9751 数模转换器中的模拟和数字部分各有自己独立的供电电源(AVDD和DVDD),因而可以独立地在2.7V~3.6V的工作范围内工作。它的数字部分包括边沿触发锁存器和分段译码逻辑电路。而模拟部分则包括PMOS电流源及其相关的差分开关,以及1.2V的带隙电压基准和一个基准电压控制放大器。

AD9751的满刻度输出电流由基准控制放大器决定,它通过调节一个外部电位器可使电流在2mA~20mA的范围内变化。而用外部电位器,基准控制放大器和电压基准VREFIO可组合设定基准电流IREF。AD9751的满刻度电流IOUTFS是IREF的值的32倍。

4 、应用设计

4. 1 基准电压

AD9751内含一个1.2V的带隙基准电压。使用内部基准时,在引脚REFIO和ACOM之间接0.1μF的电容可达到去耦的目的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)