基于FPGA 的嵌入式图像检测系统因其快速的处理能力和灵活的编程设计使得它在工业现场的应用非常广泛,通常这些系统都是通过采集图像数据流并对它实时处理得到所需的 特征信息。图像数据的获取是整个系统的第一步,作为整个系统的最前端,它决定了原始数据的质量,是整个系统成功的关键。CMOS 图像传感器采 用CMOS 工艺,可以将图像采集单元和信号处理单元集成到同一块芯片上,因而在集成度、功耗、成本上具有很大优势,这使得它在嵌入式图像处理领域的运用越来越多。 CMOS 图像传感器芯片大都把 I2C 总线的一个子集作为控制接口,用户可以很方便地对芯片进行编程 *** 作,根据设计要求的不同配置图像传感器内部寄存器数据,以获取期望的图像。本文以 ApTIna 公司的MT9P031 图像传感器为例,用Verilog 硬件描述语言设计了I2C 总线的接口电路,以FPGA 作为核心控制器实现了对MT9P031 初始化 *** 作,不仅验证了I2C 总线的配置效果,得到了理想的图像数据,还为后续线结构光图像的处理系统奠定了基础。

1 I2C 总线协议及MT9P031 配置过程介绍

1.1 I2C 总线协议

I2C(Inter-Integrated Circuit Bus) 总线是由PHILIPS 公司开发的两线式用于芯片之间连接的总线,由于其接口线少,控制方式简单,通信速率较高等特点,在单片机、串行EEPROM 等器件中有着广泛的使用。I2C 总线用两根信号线来进行数据传输,一根为串行数据(SDA, Serial Data),另一根为串行时钟线(SCL, Serial Clock)。若干兼容器件(如存储器、A/D、D/A、LCD 驱动器等)可以共享I2C 总线。I2C 总线上所有器件依靠SDA 发送的地址信号寻址,不需要片选线。任何时刻总线只能由一个主器件控制,各从器件在总线空闲时启动数据传输。

1.2 MT9P031 配置时序分析

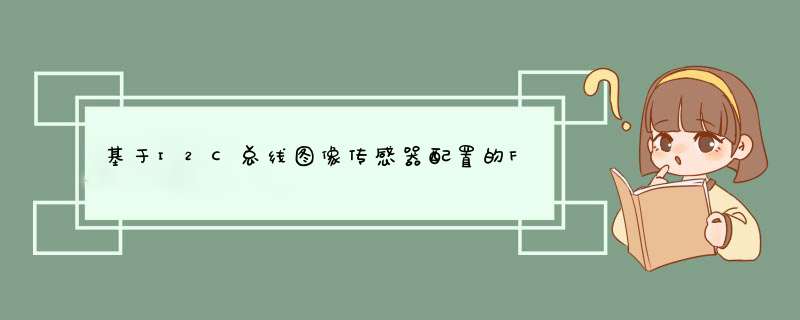

由 于检测系统需求的不同,图像传感器可能要工作在不同的模式,因此需要通过外部控制器对其内部寄存器进行读写 *** 作,完成具体的配置。典型的写MT9P031 寄存器时序如图1 所示,起始信号过后,FPGA 先写入设备(即MT9P031)的地址0xBA,然后释放SDATA 数据总线,随后MT9P031 返回一个应答信号ACK,FPGA 获取应答信号后,经过一个时钟周期再传送待配置的寄存器地址0x09,在获取应答信号后再传送16 位的寄存器数据,由于每次只能发送8 位数据,所以这16位的寄存器数据要分两次才能发送完毕,先发送的是高八位数据,后发送的为低八位数据,每发送完一个字节的数据,FPGA均会获取一位的 应答信号,然后结束一个传送周期,完成一个寄存器的配置,即IDAddress+ SUB-Address + W-Data 总共32位的数据。重复上述过程可以对不同的寄存器进行不同的参数配置。

图1 写MT9P031 时序图

2 FPGA 模块设计

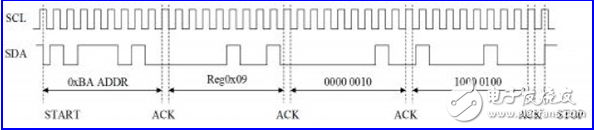

为 了实现对图像传感器的正确配置,必须严格按照MT9P031 的配置时序完成设计,本设计中I2C 总线配置模块主要由三个小模块构成,它们分别是I2C_Clock_Generator、I2C_Controller 和Register_Value,各模块之间的连接如图2 所示。

图2 I2C 总线配置模块结构框图

I2C_Clock_Generator 主要产生负责产生I2C 串行时钟信号,根据协议数据传输有三种速度模式:正常模式100Kb/s、快速模式400Kb/s、高速模式3.4Mb/s,为了保证配置的准确性和成功 率,设计中采用了100Kb/ 的速度模式,即SCLK 的频率为100KHz,因为FPGA 外部输入的时钟为50MHz,所以需要对其分频获得。同时该模块还负责产生数据传输有效信号,保证SDAT 的改变发生在SCLK 的低电平时段。

Register_Value 其实一个查找表,负责保存MT9P031 内部需要配置的寄存器地址和数据,查找表内数据的位数都是24bit,单独作为一个模块的目的是为了方便用户改变配置数据,决定图像传感器的不同工作状态。

I2C_Controller 是图像传感器配置设计的核心模块,主要完成了启停命令产生、字节发送和读取、应答信号采集等功能。同时,I2C_Controller 模块还产生I2C读写时序,由状态机严格按照I2C 协议实现,将Register Value 部分送出的24 位 *** 作码I2C_DAT 转化成为正确的I2C 时序。一个寄存器的数据传输完成后,模块还将判断寄存器配置数据是否发送顺利,如果一切正常,LUT_INDEX 信号会自动加一,控制Register Value 查找表产生下一个寄存器的地址和数据。

3 I2C 接口的仿真及调试

为了验证MT9P031 配置过程中I2C时序的正确性,本设计在Modelsim Se10.1c 版软件平台中对整个模块进行了功能仿真,在Test bench 中模拟了50MHz 控制时钟以及复位信号,观察最终输出端的波形情况。图3 是对MT9P031 的寄存器地址0x00 进行读 *** 作的仿真波形图,图4是对寄存器地址0x01 写入0x01EA 的仿真波形图。

图3 读取寄存器0x00 的波形仿真

图4 向寄存器0x01 写入数据0x01EA 的波形仿真

4 总结

基于I2C总线的 图像传感器配置在视频图像采集处理系统中非常普遍,本设计结合了FPGA 的可编程特性,采用模块化的方法设计方法完成了I2C 配置电路的设计,详细介绍了各个模块的设计流程和实现方式,最后对整个设计进行了仿真,验证了设计的正确性。综合调试后占用资源极小,可靠性高,而且利用 Verilog 硬件描述语言的设计使得可移植性很强,具有广泛的应用价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)