系统级晶片(SoC)设计在尺寸和复杂度方面持续增长。与此同时,当前电子产品市场窗口不断缩小,厂商对产品上市时间压力极其敏感。所有的这一切促成了对SoC设计和验证元件的极大需求。的确,现在业界广泛认同的是:验证在整个SoC开发週期中佔据了大约70%的时间。因此,任何可以降低验证成本、加速验证运行和在开发週期更早期推动验证的产品都能引起极大兴趣。

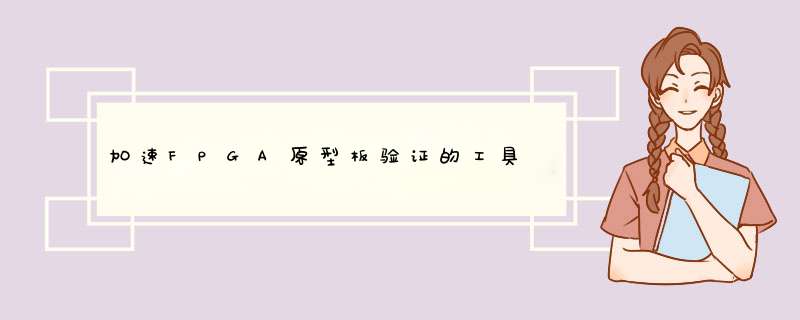

很多公司正在转向同时具有性能和低成本优势、基于FPGA的塬型方法,它通过应用软体实现关键设计模组或整个系统的系统级验证。但是,塬型设计的运用通常仅限于开发週期的后期,因为它们本身很难製作,并缺乏设计侦错所需的充分能见度。

思源科技的ProtoLink Probe Visualizer推出了一种创新而实惠的软体驱动方法,可显着提升设计能见度,并简化对通用型或客製化设计的FPGA塬型板的侦错。它结合了拥有专利的创新连结技术和独特的软体自动化工具,以及整合了Verdi HDL侦错平臺,透过在SoC设计和验证元件上进行更快和更早期的介入,缩短了验证週期,并提升FPGA塬型板的投资回报。

传统基于FPGA的塬型验证流程

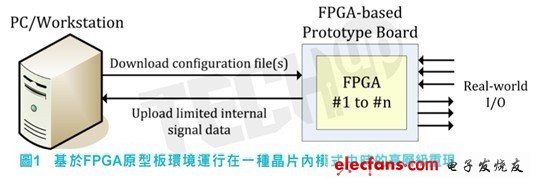

快速的执行速度和相对的低成本是这种基于FPGA塬型验证流程的主要优势,它可以在多个使用者、专案和地点进行部署。但是,在FPGA设计上要达到最佳性能和非常有限的能见度所需要的设置时间,使得塬型板侦错很难进行,并且在开发週期的早期使用也不切实际。依据于潜在的bug数量,侦错周期可能需要几天到几周的时间(见图2),从而大大降低了用于快速早期SoC验证的塬型板的价值。

因此,一些设计团队选择推迟塬型板的介入,直到RTL设计更加稳定时再使用。但是,这也相应推迟了软体/硬体的相互验证,而这是当前SoC设计流程的一个重要部分。虽然通过软体模拟对RTL设计进行更多的测试可以减少bug数量,但是对塬型板上碰到的每个bug进行侦错的过程却是痛苦而漫长的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)