把相对成熟的技术应用到某些特定领域如通讯,视频,信息处理等等开发出满足行业需要并能被行业客户接受的产品这方面主要是FPGA技术和专业技术的结合问题,另外还有就是与专业客户的界面问题产品设计还包括专业工具类产品及民用产品。FPGA因为具备接口,控制,功能IP,内嵌CPU等特点有条件实现一个构造简单,固化程度高,功能全面的系统产品设计将是FPGA技术应用最广大的市场,具有极大的爆发性的需求空间产品设计对技术人员的要求比较高。为解决相关FPGA工程师及爱好者提供相关实际案例和电路参考,电子发烧友网隆重整合推出《FPGA设计实例全攻略》系列,后期会陆续推出相关章节,以飨读者,敬请关注。

一、远程在线更新FPGA程序的方法

1 概述

现场可编程门阵列(Field Programmable Gate Array,FPGA)器件具有高密度、低功耗、高速、高可靠性等优点,在航空航天、通信、工业控制等方面得到了大量应用。FPGA的处理器分为软核和硬核,并且软核处理器具有高度的灵活性和可配置性。

由于FPGA器件采用的是SRAM工艺,在断电的情况下FPGA内的配置数据将丢失,所以需要非易失的存储器来结合FPGA完成嵌入式系统的设计。EPCS(Erasable Programmable Configurable Serial)Flash属于串行接口Flash,具有接口简单、体积小、配置方便的特点,通常用来存储FPGA的配置文件和NiosII的软件可执行代码。在经过合理的配置后,系统在上电后就可以从EPCSFlash中读取这些文件来启动整个系统。

为了能使系统得到更灵活的应用,充分发挥FPGA的灵活性、高效性,FPGA的软硬件程序都需要方便的更新和升级功能;而当形成产品后,通过JTAG和NiosII IDE工具来联合完成对EPCS Flash的更新烧写很不方便。为此,本文结合Altera公司提供的工具,提出了一种远程在线更新FPGA配置文件和NiosII程序文件的方法。

2 系统硬件结构

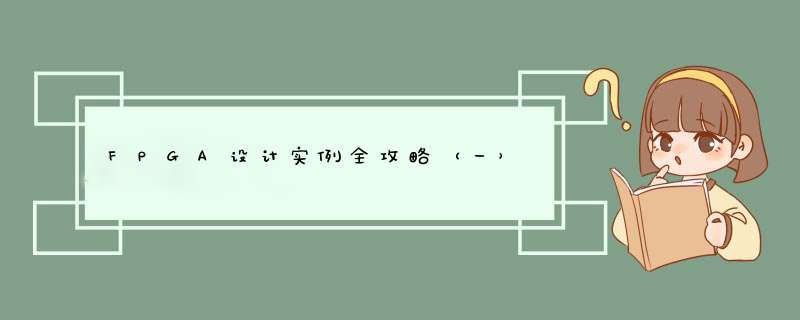

系统硬件结构如图1所示。系统主要有上位机系统、FPGA系统、EPCS Flash三个主体部分。上位机系统提供人机交互的部分,FPGA系统包括NiosII处理器、EPCS控制器、网络及串行接口和其他外部接口,EPCSFlash主要用于存储FPGA的配置文件和Nios程序映像文件。上位机系统通过FPGA集成的网络及串行接口来完成通信工作。

FPGA采用Altera公司的CycloneIII系统的EP3C40F48417N芯片。它具有低功耗、高集成度、易于使用的特性。EPCS Flash采用Altera公司的EPCS16SI16N芯片,它支持多种可配置的时钟源,最高支持100 MHz的外部时钟源,具有16 Mb的存储空间,足够满足一般的FPGA配置文件和Nios程序文件的存储需要。

3 更新程序处理流程

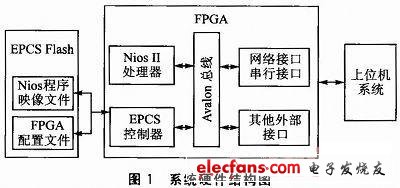

更新FPGA的配置文件和NiosII的应用程序的流程如图2所示。

本方法把由NiosII IDE生成的FPGA配置文件和NiosII程序文件合并,并编程为一个可以直接执行的、包含FPGA配置文件和NiosII程序文件的二进制BIN文件。然后把该文件通过X-modem协议由上位机系统传输给NiosII的应用程序。NiosII的应用程序接收到完整的BIN文件后,把该BIN文件写入到EPCS Flash中。最后,Nios II的应用程序停止看门狗,程序重新启动,即完成了FPGA的远程在线更新程序的过程。

4 合并程序文件

Nios II的启动要经历两个过程:

①FPGA器件本身的配置过程。如果内部逻辑中使用了NiosII,则配置完成的FPGA中包含有NiosII软核CPU。

②NiosII本身的应用过程。一旦FPGA配置成功后,NiosII就被逻辑中的复位电路复位,从reset地址开始执行代码。

Nios II IDE将FPGA的配置文件(.sof文件)和应用程序(.elf文件)转成flash格式文件,转换后的flash格式文件是一种S-Record格式数据,包含如下区域:《type》《length》《address》《data》《checksum》。各字段的意思分别如下:《type》表示记录的类型;《length》表示数据的长度;《address》表示数据写入的起始地址,该字段的长度取决于《type》的取值;《data》表示存储的数据;《checknum》表示校验位。

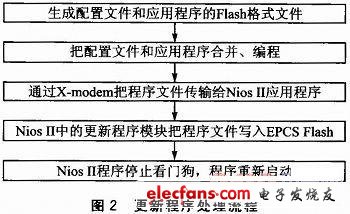

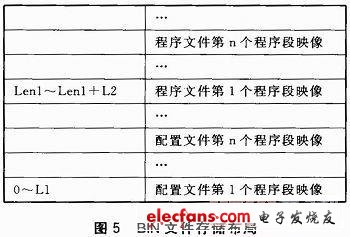

配置文件和应用程序可能有多个段,每个段前面都插有一个“程序记录”。一个“程序记录”由2个32位的数据构成,一个是32位的整数,另一个是32位的地址,分别表示程序段本身的长度和程序段的运行时地址。其存储布局如图3所示。

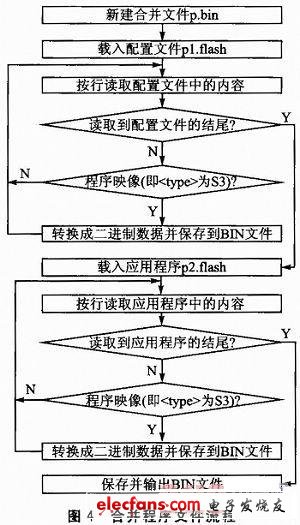

为了在更新程序时把FPGA配置文件和Nios II应用程序一起更新,把FPGA配置文件和Nios II应用程序合并成一个文件,并且把合并后的Flash格式的文件转换成不需要地址解码就能直接执行的二进制BIN文件。具体处理流程如图4所示。

在合并程序的过程中,去掉了flash文件中的长度、目的地址等用于解析程序的信息,并且把程序映像由字符格式转换为二进制格式。合并后的BIN文件包含FPGA配置文件和Nios II应用程序,并且Nios II应用程序紧挨在FPGA配置文件的后面,其存储布局如图5所示。

5 Nios II更新程序模块处理

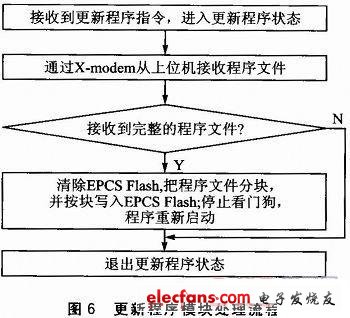

Nios II程序中的更新程序模块主要负责从上位机接收合并后的可执行BIN文件,并把该BIN文件写入EPCSFlash,处理流程如图6所示。

5.1 程序文件的传输

Nios II应用程序中的更新程序模块和上位机系统采用X-modem协议传输程序文件,X-modem协议是一种网口和串口通信中广泛用到的异步传输协议。

如果在程序传输过程中出现错误,更新程序模块能够通过设置超时来退出更新程序的状态。

5.2 对EPCS Flash的读写

由于EPCS Flash的串行配置器件定义了特殊的读写协议,所以Nios II程序只能通过Altera提供的HAL API(ApplicaTIon Program Inter face,应用程序接口)来完成读写Flash。打开、关闭Flash设备的API为:alt flash open_dev()和alt_flash_close_dev()。 *** 作Flash读写

的API为:alt_read_flash()和alt_write_flash_block()。清除Flash的API为alt_erase_falsh_block()。

结语

本文以提高FPGA远程更新程序的方便性为目标,提出了一种基于EPCS Flash的远程在线更新FPGA程序的方法,从而在应用中能够使基于FPGA的产品更加方便地维护升级。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)