随着现代电子技术的发展,FPGA具有系统结构和逻辑单元灵活、集成度高以及适用范围宽等特点,可以很好地解决这个难题。因为FPGA采用的是硬件并行算法,能很好的解决速度和实时性的问题,并且其具有灵活的可配置特性和优良的抗干扰能力,使得FPGA构成的数字信号处理系统非常易于修改、测试及硬件升级。随着FPGA技术的不断成熟,其内嵌资源不断丰富,硬核乘法器和块RAM的数目不断增长,使得FPGA实现复杂的数字信号处理算法变得更为简单和快速。因此,本文对FPGA技术和Kalman滤波算法进行结合研究,探索Kalman滤波算法在FPGA中的实现方式并进行性能验证,以对基于FPGA的Kalman滤波算法的工程实现提供参考。

1 Kalman滤波算法理论

Kalman滤波是在时域内以信号的一、二阶统计特性已知为前提、以均方误差极小为判据,能自动跟踪信号统计性质的非平稳变化,具有递归性质的一种算法。它处理的对象是随机系统,并能正确估计出有用信号。设离散系统差分方程如下:

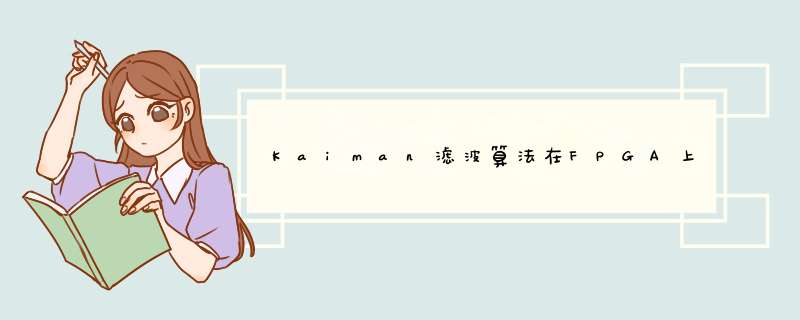

则Kalman滤波方程组如下:

状态一步预测方程:

从式(1)~(6)可知,若利用传统的处理器实现Kalman滤波算法,由于其指令执行的顺序性,至少需要分为5步来实现,其中每一步还都需要进行至少1次的加法和乘法等运算,每次运算都要顺序执行,其执行速度和效率很低;如果利用FPGA来进行Kalman滤波,根据其各步的逻辑关系,可以分为3步来实现,即第一步计算状态一步预测值 和一步预测均方误差Pk+1/k,第二步计算滤波增益Kk+1,第三步计算状态最优估值

和一步预测均方误差Pk+1/k,第二步计算滤波增益Kk+1,第三步计算状态最优估值 和估计均方误差Pk+1/k+1。由此可知,利用FPGA技术可以实现Kalman滤波的并行计算,压缩计算时间,提高解算速度。因此,对FPGA的Kalman滤波进行研究开发,可实现基于FPGA的快速Kalman滤波解算,满足在对实时性要求更高的环境中使用。

和估计均方误差Pk+1/k+1。由此可知,利用FPGA技术可以实现Kalman滤波的并行计算,压缩计算时间,提高解算速度。因此,对FPGA的Kalman滤波进行研究开发,可实现基于FPGA的快速Kalman滤波解算,满足在对实时性要求更高的环境中使用。

2 在FPGA中实现Kalman滤波算法研究

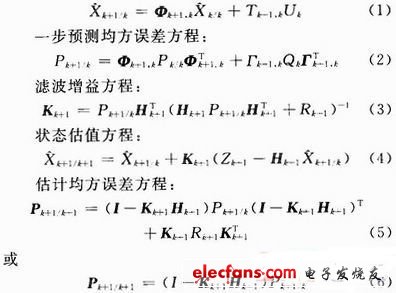

由于FPGA实现Kalman滤波解算速度非常快,若利用FPGA的串行口依次输入观测值,由于数据串行输入的特点,会使FPGA的解算部分等待数据接收完毕才能执行滤波解算,导致整体的解算时间过长。为检验FPGA实现Kalman滤波器的计算性能,本文预先将观测值输入并保存于FPGA内的ROM中,以使FPGA可以连续地进行滤波解算,实现方案原理如图1所示。

图1中,Kalman滤波解算在FPGA内完成,RAM和ROM使用FPGA内嵌的硬件RAM存储器,其中RAM暂存每步的中间结果,ROM存放滤波中的固定系数,如观测矩阵、噪声系数阵等。Kalman滤波的解算过程主要利用内嵌的硬核乘法器等资源来完成。因解算速度较快,解算结果暂存于一个稍大的存储器内,同时通过串行口输出到PC机上保存用于分析。该方案的关键问题是在FPGA中实现Kalman滤波算法。

FPGA实现Kalman滤波器,其实质就是控制数据的转移和存储并实现矩阵的相乘、加、减、求逆等运算。其中,数据的转移控制需要有限状态机(FSM)来完成,同时FPGA设计中,不可避免的会遇到资源与速度的问题。因此,需要对上述各关键技术进行研究和实现。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)