引言

现代通信技术正走向网络核心技术分组化、窄带接入技术无线化。现在无线作为有线的有效补充,得到了越来越广泛的应用,在很多场合,许多多媒体应用需要短距离的无线传输。无线多媒体系统除了提供多媒体服务外,具有无线所具有的建设速度快、安装灵活方便等优点,还能在布线困难的地方实现多媒体通信。因此,无线多媒体具有广阔的应用前景。但无线也存在着一系列的问题,如多经传输、信道衰落和空间射频干扰等。

1无线多媒体系统概述

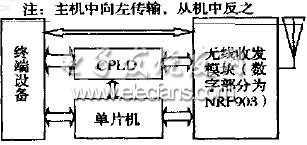

本系统为无线可视系统,集图像、声音、控制、数据等多媒体信息的采集、传输和处理为一体,系图1无线多媒体系统框图统能传输单向视频信号,双向语音信号,双向数据信号,并具有数据采集等功能。系统框图如图1所示,系统分为主机和从机。通过对主从机的参数设定可以实现点对点和点对多点通信。主从机之间可以实现实时的双向语音通信,同时从机把视频信号传给主机,从机还可以把传感器等的数据传给主机。

图1无线多媒体系统框图

2系统设计

2.1NRF903芯片介绍

射频收发电路采用NordicVLSI公司的单片射频收发芯片NRF903。该芯片的工作频率为国际通用的ISM频段433/868/915MHz,NRF采用抗干扰能力强的GMSK调制方式来优化信道效率,在GMSK中,在调制载波前采用了高斯滤波器,这样可以在同等带宽下传输更高速率的数据,可在155.6kHz的有效带宽下传输最高76.8kbps的数据。最大发射功率可以调整到+10dBm,天线接口设计为差分天线。NRF903的工作电压范围为2.7~3.3V,NRF还具有待机模式,这样可以更省电和高效。芯片的参数包括工作频率和发射功率都可以通过一个14bit的配置寄存器用SPI串行线进行设置。采用DSS+PLL频率合成技术,频率稳定性极好;灵敏度高,达到-100dBm.内置独有的镜像频率抑制电路。

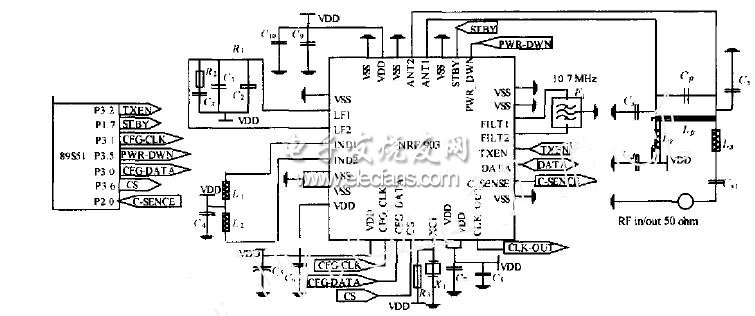

2.2射频模块电路设计

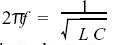

为了提高发送距离,本系统中的NRF903模块采用拉杆天线,如图2所示,有效值的设定才能保证良好的功能,根据公式 在不同的PCB板的模块调试中,选定CS,CP,LP的参数值使电路谐振在所工作的频段,同时使LS,CS1发生谐振。所选定的电容、电感必须具备良好的性能。PCB的底面有一个连续的接地面,射频电路的元件面以NRF903为中心,各元器件紧靠其周围,尽可能减少分布参数的影响。射频部分的电源与数字电路部分的电源分离,NRF903的VSS端直接连接到接地面。注意不能将数字信号或控制信号引入到PLL回路滤波器元件上。NRF903的VCO电感位置的最佳设计是保证产生1.1±0.2V的PLL回路滤波器电压。

在不同的PCB板的模块调试中,选定CS,CP,LP的参数值使电路谐振在所工作的频段,同时使LS,CS1发生谐振。所选定的电容、电感必须具备良好的性能。PCB的底面有一个连续的接地面,射频电路的元件面以NRF903为中心,各元器件紧靠其周围,尽可能减少分布参数的影响。射频部分的电源与数字电路部分的电源分离,NRF903的VSS端直接连接到接地面。注意不能将数字信号或控制信号引入到PLL回路滤波器元件上。NRF903的VCO电感位置的最佳设计是保证产生1.1±0.2V的PLL回路滤波器电压。

元器件值的选定见文献[1],根据不同的PCB板以及相关器件特性,根据频谱分析和测定的电压等值,可以适当的调整这些元器件的值,使其性能达到最佳。模块如图2所示CFG-CLK,CFG-DATA,CS为初始化配置线。STBY为待机模式控制端,“0”为工作模式,“1”为待机模式。CLK_OUT为分频时钟输出。C_SENSE为载波检测输出,当没有接收到载波信号时,C_SENCE输出电压为“0”,随着接收电平的上升,C2SENCE的输出电压上升,上升到输入电平值接近接收灵敏度极限以上10dB点时,C_SENCE为“1”。TXEN为发射控制端,“0”为接收模式,“1”为发射模式。DATA端为数据输入?输出端。PWR_DWN为掉电模式控制端,“0”为工作模式,“1”为掉电模式。其余的引脚为VCC和VSS。

图2射频模块电路框图

2.3初始化程序设计

在NRF903模块正常工作前,需对其内部14bit的控制寄存器通过CFG_CLK,CFG_DATA,CS进行初始化。CS,CFG_CLK和CFG_DATA组成的串行接口将控制参数锁存到内部配置单元的移位寄存器中。芯片选择脚(CS)用来使能芯片的配置模式。配置期间,CS为高,配置字被锁入(MSB在先)。配置字被锁入移位寄存器后,CS变低,配置开始启动。配置时序见文献[2]。

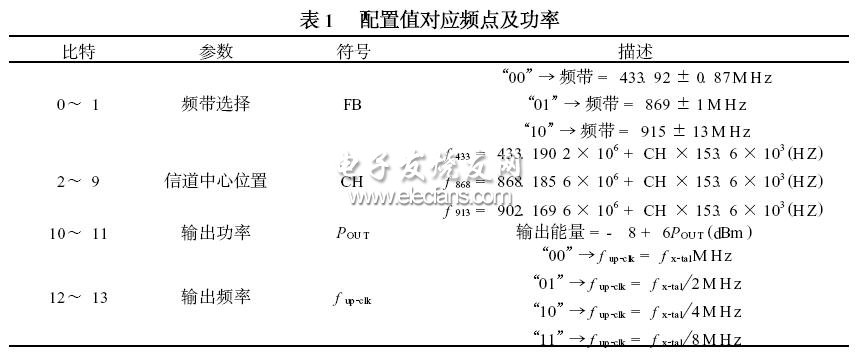

CFG_DATA位速率不能超过1Mbps。一旦配置完,设备状态由外部信号TXEN,PWR_DWN,STBY和DATA(DATA在发射模式为输入脚,在接收模式为输出脚)来设定。配置可以在除了待机和掉电以外的所有模式中完成。在掉电和待机模式工作后,寄存器内容仍然有效。配置数据只有当电源撤除后才会丢失。如果不进行配制,模块在默认模式下,工作频率为868.1856MHz,按最大功率输出,CLK_OUT为1.3284MHz。该特性使微控制器的软件调试变得简单、方便。配置中的1~2位为频段选择,3~10位为频点选择,11~12为输出功率设置,13~14为时钟分频输出设置,如表1所示。

在本系统中,工作频段为927M,选择的配置字为1000,0010,0100,10。初始化程序如下:

CLRP3.5;PWN-DWN=0,置工作模式

CLRP1.7;STBY=0,置工作模式

MOVR3,#08H

MOVA,#82H

SETBP3.6;配置期间CS拉高

CFG1:RLCA

MOVP3.0,C;

CLRP3.1

SETBP3.1

DJNZR3,CFG1

MOVR3,#06H

MOVA,#48H

CFG2:RLCA

MOVP3.0,C

CLRP3.1

SETBP3.1

DJNZR3,CFG2

CLRP3.6;CS置低,配置结束。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)