AHB总线规范是AMBA总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。

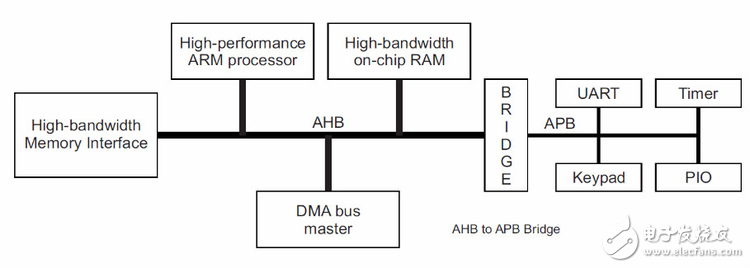

1.1 AHB总线的架构AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。

下图是一个典型的AHB系统总线的结构示意图

1.2 AHB基本特性

Burst传输

Split事务处理

单周期master移交

单一时钟沿 *** 作

无三态

更宽的数据总线配置(64/128)

流水线 *** 作

可支持多个总线主设备(最多16个)

2. AHB总线的组成

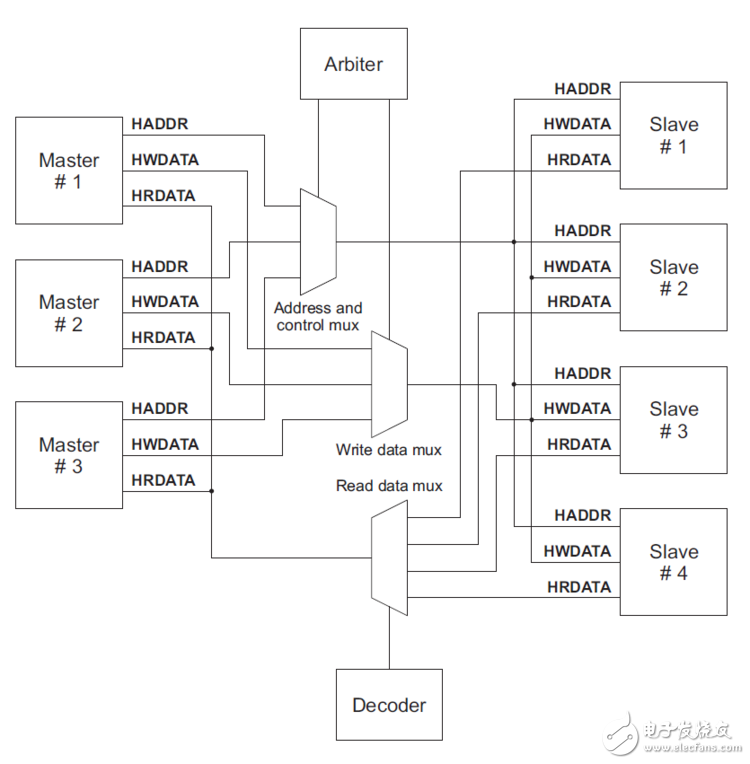

AHB总线由Master、Slave和Infrastructure构成。Infrastructure由arbiter、数据多路、地址控制多路、译码器构成。

主设备Master

发起一次读/写 *** 作

某一时刻只允许一个主设备使用总线

从设备Slave

响应一次读/写 *** 作

通过地址映射来选择使用哪一个从设备

仲裁器arbiter

允许某一个主设备控制总线

译码器decoder

通过地址译码决定选择哪一个从设备

总线可以分为三组

写数据总线(HWDATA)

读数据总线(HRDATA)

地址控制总线(HADDR)

Name Source To DescripTIon

HCLK clock source 各module 总线时钟,上升沿采样

HRESETn reset controller 各module 总线复位,低电平有效

HADDR[31:0] Master decoder

mux to slave

arbiter 32位系统地址总线

HTRANS[1:0] Master mux to slave 当前传输类型NONSEQ, SEQ, IDLE, BUSY

HWRITE Master mux to slave 1为写,0为读

HSIZE[2:0] Master mux to slave 每一个transfer传输的数据大小,以字节为单位,最高支持1024位

HBURST[2:0] Master mux to slave burst类型,支持4、8、16 burst,incremenTIng/wrapping

HPROT[3:0] Master mux to slave 保护控制信号,需要slave带保护功能,一般不用

HWDATA[31:0] Master mux to slave 写数据总线,Master到Slave

HRDATA[31:0] Slave mux to master 读数据总线,Slave到Master

HREADY Slave mux to master

arbiter 高:Slave指出传输结束

低:Slave需延长传输周期

HRESP[1:0] Slave mux to master

arbiter Slave发给Master的总线传输状态OKAY, ERROR, RETRY, SPLIT

HSELx Decoder slave slave选择信号

AHB仲裁信号

Name Source To DescripTIon

HBUSREQx Master arbiter master给仲裁器的请求获得总线使用权的请求信号,最多支持16个master

HLOCKx Master arbiter 如果一个master希望自己在传输期间不希望丢掉总线,则需要向仲裁器发送这个锁定信号

HGRANTx arbiter master 授权信号,当前bus master x的优先级最高。当HREADY和HGRANTx同时为高时,master获取系统总线的权利

HMASTER [3:0] arbiter 具有split功能的slave 仲裁器为每一个master分配的ID,指出哪个主设备正在进行传输,提供进行split的信息

HMASTLOCK arbiter 具有split功能的slave 表示当前的master正在执行Locked *** 作。这个信号和HMASTER有这相同的时序

HSPLITx[15:0] slave arbiter 从设备用这个信号告诉仲裁器哪个主设备运行重新尝试一次split传输,每一位对应一个主设备

有需要占用总线的Master向arbiter发出请求,arbiter授权给指定的master。任一时间周期只有一个master可以接入总线,对其指定的slave进行读写 *** 作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)