作为下一代STA工具,Tekton提供了突破性的单CPU多模/多角性分析性能,能够在几分钟内为上千万单元级的电路提供时序更新。同时,它还完全支持串扰分析和AOCV分析,并且内嵌了一款可在有极高精度要求时使用的SPICE引擎。

时序分析已成为了许多芯片设计团队一大瓶颈。随着设计尺寸常常突破1000万门且需要进行多个工作情景的分析,这些均给设计进度带来严重影响。设计团队被迫要么增加硬件和STA许可的投入,要么减少角点和限制所分析情景的数量,以此来应对当前静态时序分析(STA)解决方案的局限性。这些方法不仅费用昂贵且还不可扩展。设计团队需要的是快速、高容量的时序分析解决方案,它要能在几分钟内,而不是几小时或几天时间内,在标准硬件上提供签核质量时序分析。

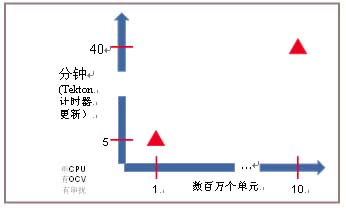

Tekton是专为解决40纳米、28纳米及更小尺寸设计需求而构建的一款STA工具。采用Tekton,设计团队能在几分钟时间内在单CPU设备上运行具有多个情景的超大型设计。Tekton在单一CPU上提供数量级的性能改善,同时它还完全支持多线程,用于多CPU设备上时还可提供更快的性能。跨多 CPU的近线性性能扩展使得Tekton可很好地扩展用于未来具有数亿门级电路的设计。

Tekton通过包含进一款内嵌式SPICE引擎,将验证精度标准提高到了一个新的层次。这款集成化引擎使得设计团队无需增加太多运行时间即可将先进片上变异(advanced on-chip variaTIon,AOCV)与基于路径的分析和SPICE很好结合在一起。Tekton已被架构成为下一代时序分析平台,提供了业界最精确的时序分析引擎。

几分钟内完成快速、高容量STA

Tekton提供了突破性的速度和容量,可应对40纳米、28纳米及更小设计尺寸的复杂问题。基于新的架构,Tekton提供了同类最佳的单CPU性能和支持多达24个CPU的近线性性能扩展。拥有这种架构,Tekton有能力在一小时以内在单CPU上完成一次包括OCV和串扰分析在内的完整时序分析。其独一无二的CPU性能使其完全区别于业界其它STA工具。

Tekton在几分钟内在标准硬件上提供签核质量时序分析。

可与现有STA流程兼容

Tekton提供了一款易于使用的STA环境。除了支持所有SDC版本和微捷码Tcl以外,Tekton还支持所有现有STA流程脚本。它为用户提供了灵活的查看报告方式,用户可以选择微捷码可配置格式或芯片设计团队所熟悉的格式查看时序报告。

单设备多模/多角分析可随着情景增加而线性变化

当今的复杂设计要求跨大量模式和PVT角点的时序分析。Tekton的一个主要功能就是提供在单CPU或多CPU设备上运行所有时序情景的能力。不同于现有解决方案要求一个情景有一台设备和一个许可的分布式方案,Tekton能在单台设备上运行大量情景。为达成这一目标,设计师使用单个STA脚本,将所有时序SDC、库和SPEF文件输入到运行于单台设备的Tekton中。

AOCV最大程度降低时序容限影响

设计师在设计中加入时序容限已有好几年时间。随着工艺尺寸的持续缩小,容限让时序收敛变得更为困难,大大延长了设计时间。当设计团队接触28纳米工艺时,AOCV将被视为一种能潜在地减轻OCV悲观倾向的方法。Tekton完全支持AOCV。设计师能够通过读入缩减表或通过命令行输入的方式缩减时钟或数据路径。

集成SPICE引擎,实现关键路径分析

尽可能快地实施工程变更单(ECO)是按时达成时序收敛的关键。Tekton提供了超快时序迭代,加快ECO周期。当设计团队接近最处一组时序违规时,往往其设计会处于一种‘时序或面积干扰会加大晶粒尺寸和/或延长设计时间表’的状态中。Tekton的内嵌式SPICE引擎使得用户只需最少代价即可进行关键路径的完全SPICE精度分析。

STA和提取引擎的紧密集成

实现工具与分析工具的分离是28纳米精度水平降低的原因所在。缩小布局布线、提取和STA间差距可提供快速时序收敛所需精度。Tekton和QCP提取工具是基于相同架构的独立工具。采用这种一致的架构,设计师可通过使用QCP产生的二进制格式的SPEF,缩短STA运行时间。或者,设计师还可在 Tekton会话期间,使用QCP直接从微捷码Volcano™中提取寄生参数。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)