近些年,针对智能管理的研究越来越广泛,采用的技术也越来越多,如基于单片机开发的智能监控平台[1]、在Linux内核下的智能仪器开发[2]、对智能管理的某一个方面进行研究[3]等。随着嵌入式核心芯片的高速发展,传统嵌入式系统的设计方法也随之改变,嵌入式系统逐渐由板级向芯片级过渡,即片上系统(SoC),进而发展至如今流行的可编程片上系统(SoPC)。本文就是通过超大规模FPGA和功能复杂的IP核来实现一个可编程片上系统,此系统利用可编程器件内的可编程资源以及专用硬核,构建处理器、存储器、逻辑电路和其他专用功能模块,并在智能管理软件和算法的配合下完成智能管理的各项功能。

所谓智能管理,就是以人类智能结构为基础,系统研究人与组织的管理活动规律和方法的一门学科,具有很强的实践性和扩展性,体现在本文中就是通过系统本身的智能化 *** 作而非人工干预的手段去执行其在运行过程中所遇到的诸如检测和控制等行为。对于本系统来说,其主要功能就是系统监测、综合处理,并依靠事先确定的阈值和准则实施相应的控制。其中包括对各关键模块的工作状态进行监控,对风机与电源的运行状态进行管理,并对系统智能管理过程中所得到的一些信息通过以太网上报给上位机等。

1 硬件系统构成

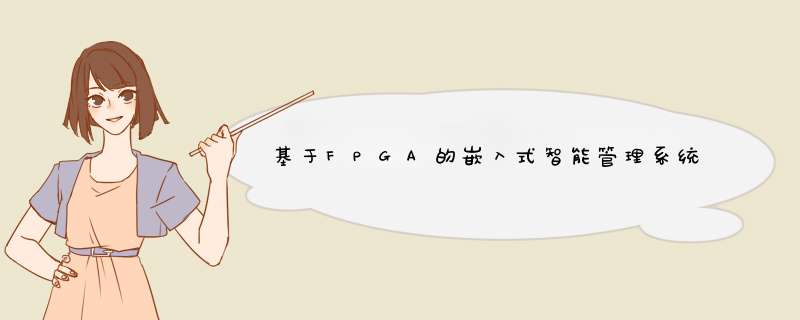

1.1 FPGA内部硬核系统构成

FPGA片内结构如图1所示,FPGA片内所有模块包括PPC405处理器、MAC核、I2C核、GPIO核及URAT核,都连接到片上高性能PLB总线上,PPC405通过PLB总线来访问每个IP核,各IP核的大致作用如下:

(1)MAC核实现网络链路层硬件,与FPGA片外的PHY芯片实现网络所需的硬件;

(2)I2C核实现I2C逻辑,支持智能管理模块与各个工作模块之间的I2C总线协议,实现I2C总线的检测与控制功能,如接收各工作模块的温度等;

(4)UART核实现PPC405的串口 *** 作,将串口信息传送至主机进行系统调试。

片上系统硬件结构大致描述为:用FPGA实现I2C总线协议,并与处理模块对接;用FPGA实现1-wire单线总线协议,并与温度传感器对接;智能管理模块要求实现的网络上报功能必须用软件来实现TCP/IP协议栈;用MAC核实现链路层功能。为减少器件数量,提高可靠性,本设计采用FPGA内嵌的PPC405处理器,为此需要使用Xilinx公司的系统开发工具EDK进行软硬件协同设计。

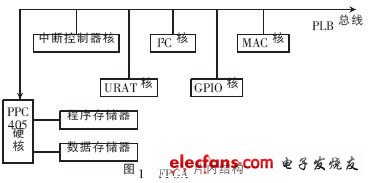

1.2 智能管理模块的构成

智能管理模块构成如图2所示。

FPGA和125电路共同实现两路1-wire总线的协议控制和电平规范,其中一路通过温度传感器来检测两个风机组内的温度。同时,另一路125芯片实现I2C总线的协议控制和电平规范,并通过I2C总线来读取机箱中各个处理模块的内部温度。FPGA通过网口与上位机进行数据通信,并通过串口对智能管理模块进行调试。FPGA通过和隔离与驱动电路连接后来控制电源,即相当于是程控开/关电源,以保护机箱中的各处理模块免于因过热而损坏。该模块仅采用12 V电源供电,模块中的其他类型的电源均通过DC-DC转换模块内部产生。

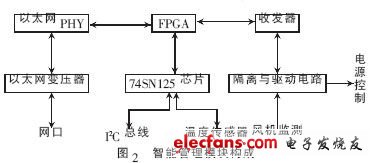

1.3 智能管理系统的构成

智能管理系统的构成如图3所示。智能管理模块作为智能管理系统的核心,执行着整个系统运行的几乎所有指令。

(1) 智能电源。多电源平衡供电的智能电源模块,具有短路、过载、过压及过热保护功能,空载可开机,并且多个电源可以并联输出。

(2)温度传感器。采用军品温度传感器,置入风机组中用于测试风机通道的空气温度。该温度传感器只有3个管脚,从右到左分别是VDD(+5 V电源)、DQ(数据信号)、GND(地线)。其中,DQ管脚符合1-wire总线协议,与智能管理模块相对接。该温度传感器的工作温度范围广、精度高、使用简单可靠。

(3)风机组。一个机箱配两个风机组,每组由7个大风机组成。每个风机都带有集电极开路输出的被检测脉冲信号,智能管理模块根据该信号是否有脉冲波形来判定每个风机是否工作。

(4)计算机。智能管理模块与计算机可以通过网口和串口两种方式进行通信,本系统给出了预留,可以任意选择,主要功能是上报各类系统数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)