摘 要 :SATA作为一种高速串行, 点对点传输的硬盘接口, 已取代了IDE 硬盘接口。 目前在硬盘中使用较为普遍的是 SATAII 和SATAIII, 其线速率分别达到了3Gbit•s -1和6 Gbit•s-1。文中对 SATAII 协议进行了全面的分析,并利用 Xilinx公司的ISE开发工具和 ML507干估板完成了协议的软 IP核编写与调试。 所用 FPGA 型号为XC5VFX70T, 利用其中硬核Rocket IO GTX 实现了高速链路的功能,并使用多级流水线技术进行并行设计以提高整体速度。

SATA作为一种高速串行链路已取代了 IDE作为 硬盘的标准接口。该高速差分链路使用吉比特传输和8B/10B 编码技术, 其相比于IDE、 PATA 接口具有传输 速度更高、 设备升级更简单和配置使用更便捷等优 势[1] 。 首先, 作为一种高速点对点的传输方式, SATA解决了直流偏置、 信号偏移、 码间干扰等问题, 并提高 了传输的带宽。 同时具备了更完善的查错和纠错能 力, 传输质量和传输可靠性得到了大幅提升。 其次,SATA接口相比于传统的并行接口具有更少的引脚数 目, 更利于PCB板级的设计、 装配和散热。 最终,SATA 总线还支持热捅拔并具有更低的功耗。SATA接口协 议具有层次化的结构[2-3] , 如图1 所示, 从下到上分别 是物理层、 数据链路层、 传输层和应用层。 其中物理层 负责低压差分信号的发送和接收, 并实现接口的初始 化过程和速率的自动协商。

在发送过程中, 物理层从链路层接收并行的数据将其转为串行数据, 然后以3Gbit•s -1 的线速度向硬盘侧发送LVDS NRZ高速比特流。在接收过程中, 将串 行数据转化成并行数据, 在串行数据流中检测其中的K28.5字符, 使得输出的并行数据对齐[4] 。 物理层提供 的具体功能如下: ( 1) 发送侧和接收侧提供100Ω 电阻 进行内部端接, 以此来消除反射, 保证信号的完整性。

( 2) 向链路层提供不同位宽的接口。

( 3) 用 CDR技术 从高速的串行比特流内恢复出时钟和数据。

( 4)K28.5字符检测, 以此来对齐接收到的数据。

( 5) 发送和检测OOB( Out-Of-Band) 信号, 进行硬盘和FPGA的同步 和协商。

( 6 ) 向上层报告物理层的工作状态。

( 7 ) 提 供电源管理功能, 以此降低功耗。

( 8 ) 支持接收和发 送阻抗匹配。

( 9) 解决扩散频谱时钟引起的输入数据 频率波动。

( 10) 响应远端发出的测试请求。

SATA 协议使用OOB信号来完成初始化过程和速 率协商过程。OOB信号不属于数据信号, 所以称之为 带外信号。OOB是一种低频信号, 具体含有3 种模 式: COMRESET、COMINIT和COMWAKE。 COMRESET, 如图2所示, 由主机端发送, 用来设备复位和链 路的初始化, 其由突发长度为106.7ns 的Align 原语 和 320ns 的空闲共模电平分隔。COMINI, 如图 2所 示, 格式与COMRESET相同, 与后者的区别在于, 其是 由设备侧向主侧发送的。COMWAKE, 如图3 所示, 与 前两者的区别在于其的空闲间隔为106.7ns, 且设备 侧和主侧均可以发送。

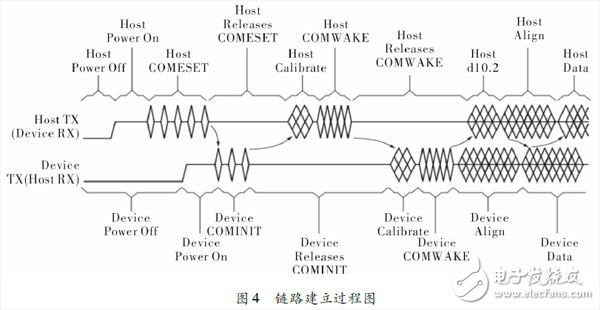

在上电和硬件复位期间, 主机通过OOB信号来建 立通行链路, 其中包括速度协商、时钟恢复、阻抗校准和 自我诊断等。 具体上电过程如图4所示, 由以下10个步骤组成:

( 1) 主侧FPGA和设备侧硬盘处于断电状态。

( 2) 系统上电, 主设备侧将发送和接收差分对拉到共 模电压。

( 3) 主设备侧发送 COMRESET信号。

( 4) 当 上电复位结束后, 主设备侧停止发送COMRESET 信号 并将 串 行 总 线 置 于 空 闲 状 态。

( 5 ) 当硬盘检测到COMRESET信号,其开始发送 COMINIT信号作为响应。 硬盘可在任何时间点通过发送COMINIT 信号来建立新 的 通 信 连 接。

( 6 ) 主设备侧进行校准且发送COMWAKE信号。

( 7) 当硬盘在其的接收线上检测到COMWAKE信号后, 其开始校准发送器。 完成校准后, 硬盘发送突发长度为6的COMWAKE信号然后连续发 送Align原语。 当连续发送 54.6μs的Align 原语后还 未收到来自主设备侧的回应, 而硬盘侧则进入错误状 态。

( 8) 当主设备侧检测到COMWAKE信号后便以所 支持的最低速率开始发送D10.2字符。 于此同时, 主 设备侧开始锁定Align原语, 当准备好便以与接收到相 同的速度向硬盘侧发送Align原语。 若在880μs内主 设备未接收到Align原语, 主设备便重新开始复位。

( 9) 硬盘锁存到 Align原语序列, 并在准备就绪后, 发送SYNC原语表明可正常运行。

( 10) 当主机侧接收到非Align原语, 链路建立完成, 则可进行正常的数据传输。

SATA 协议物理层的实现由 3 部分组成, 分别是整体流程图的设计、 时钟部分和速率协商状态转移设计。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)