Avalon 总线是一种将片上处理器和外设连接成片上可编程系统(SOPC)的一种简单总线结构。Avalon总线是一种接口方式,它规定了主从设备之间的接口方式及其通信时序。

Avalon 总线的设计目的在于:

■ 简便:提供了简单易学的协议;

■ 优化总线逻辑的资源利用:节约了可编程器件(PLD)内部的逻辑单元(LE);

■ 同步 *** 作:将PLD 上的其他用户逻辑很好的集成在一起,从而避免了复杂的时序分析;

功 能 简 介Avalon 也包括很多的功能和约定来支持SOPC Builder 软件自动产生的系统﹑总线和外设:

高于4G 的地址空间-存储器和外设可以被映射为32 位地址空间中的任何地址。同步接口-所有的Avalon信号都被Avalon 总线时钟同步。这样简化了Avalon 总线的相关时序行为并便于高速外设的集成。分离的地址,数据和控制线路-分离的,专用的地址和数据路径更便于与用户逻辑相连接。外设不需要对数据和地址周期进行译码。内置地址译码器-Avalon 总线自动的为所有外设产生片选(Chip Select)信号,大大的简化了Avalon 外设的设计。

多主设备总线结构-在Avalon 总线上可以存在多个主外设。Avalon 总线自动产生仲裁逻辑。基于向导式的配置-方便使用的图形化向导引导用户完成对Avalon 总线的配置(增加外设,确定主/从关系,定义存储器映射)。

Avalon 总线结构的自动产生是由用户在向导界面的输入来决定的。动态总线容量-Avalon 总线自动处理数据位宽不匹配的外设间传送数据的细节,便于在多种不同宽度的设备间接口。

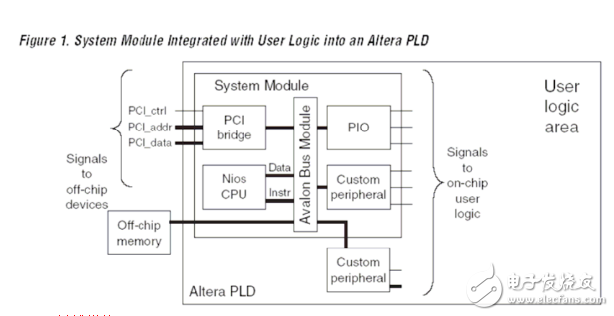

系统模块考虑在可编程芯片上实现用户自定义系统的结构,其中一部分是由SOPC Builder 自动产生的。在Altera PLD 上实现的完整系统如图1 所示。出于本文的目的,系统模块的一些部分是由SOPC Builder 自动产生的。系统模块应该包括最少一个Avalon 主外设和一个Avalon 从外设,例如UART,定时器或者PIO。系统模块的外部逻辑可以包含用户Avalon 外设及其他的和系统模块不相关的用户逻辑。系统模块必须与设计者的PLD 设计连接起来 。系统模块的端口依赖于其所包括的外设及在SOPCBuilder 中进行的设置,并随其变化。这些端口包括直接到Avalon 总线的接口及在系统模块中的用户自定义的和外设相连的接口。

Avalon 总线模块

图1. Altera PLD 上集成用户逻辑的系统模块

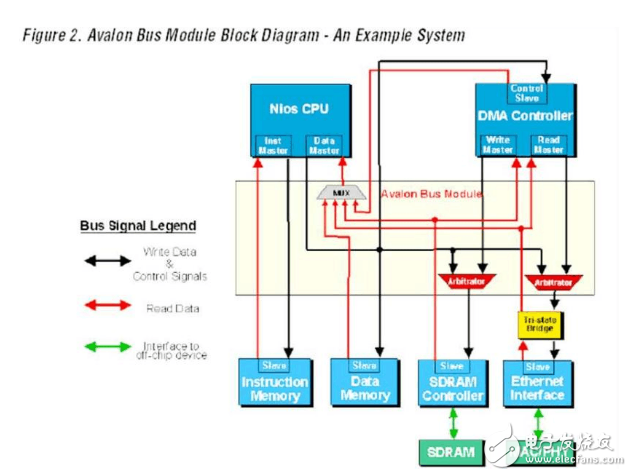

Avalon 总线模块是任何一个系统模块的“脊梁”。它是SOPC 设计中外设通信的主要路径。Avalon 总线模块是所有的控制、数据、地址信号及控制逻辑的总和,是其将外设连接起来并构成了系统模块。Avalon总线模块实现了可配置的总线结构,其可以为设计者外设之间的相互连接而改变。Avalon 总线模块是由SOPC Builder 自动产生的,所以设计师并不用亲自将总线和外设连接起来。Avalon总线模块基本上不会作为分离的单元而单独使用,因为系统设计者总是利用SOPC Builder 将处理器和其他Avalon 外设自动地集成于一个系统模块之中。设计者对Avalon 总线的注意力通常限于与用户Avalon外设相连接地具体的端口上。

Avalon 总线模块(一条Avalon 总线)是一个主动的逻辑单元,它取代了PCB 板上的被动的,金属总线。(见图2)这就是说,Avalon 总线模块的端口可以被看作是所有连接到被动总线的引脚连接。本手册只是定义了包含于Avalon 总线模块接口中的端口,逻辑行为和信号顺序,而没有提及物理总线的电气或物理的性能。

图2 .Avalon 总线模块框图-范例系统

Avalon 总线模块为连接到总线的Avalon 外设提供了以下的服务:■ 数据通道多路转换——Avalon 总线模块的多路复用器从被选择的从外设向相关主外设传输数据。

■ 地址译码——地址译码逻辑为每一个外设提供片选信号。这样,单独的外设不需要对地址线译码以产生片选信号,从而简化了外设的设计。

■ 产生等待状态(Wait-State)——等待状态的产生拓展了一个或多个周期的总线传输,这有利于满足某些特殊的同步外设的需要。当从外设无法在一个时钟周期内应答的时候,产生的等待状态可以使主外设进入等待状态。在读使能及写使能信号需要一定的建立时间/保持时间要求的时候也可以产生等待状态。

■ 动态总线宽度——动态总线宽度隐藏了窄带宽外设与较宽的Avalon 总线(或者Avalon 总线与更高带宽的外设)相接口的细节问题。举例来说,一个32 位的主设备从一个16 位的存储器中读数据的时候,动态总线宽度可以自动的对16 位的存储器进行两次读 *** 作,从而传输32 位的数据。这便减少了主设备的逻辑及软件的复杂程度,因为主设备不需要关心外设的物理特性。

■ 中断优先级(Interrupt-Priority)分配——当一个或者多个从外设产生中断的时候,Avalon 总线模块根据相应的中断请求号(IRQ)来判定中断请求。

■ 延迟传输(Latent Transfer)能力——在主、从设备之间进行带有延迟传输的逻辑包含于Avalon总线模块的内部。

■ 流式读写(Streaming Read and Write)能力——在主、从设备之间进行流传输使能的逻辑包含于Avalon 总线模块的内部。

Avalon 外设连接于Avalon 总线的Avalon 外设是逻辑器件——无论片上还是片外的——它们进行着某种系统级的任务,并通过Avalon 总线与其他的系统部件相通信。外设是模块化的系统部件,依赖于系统的需要,可以在设计的时候增加或者移除。Avalon 外设可以是存储器、处理器,也可以是传统的外设器件,如UART,PIO,定时器或总线桥。任何的用户逻辑都可以成为Avalon 外设,只要它满足本文所述的提供与Avalon 总线接口的地址、数据及控制信号接口。连接于Avalon 总线的外设将被分配专用的端口。除了连接于Avalon 总线的地址、数据及控制端口之外用户也可以自行定制端口。这些于用户逻辑相连接的信号扩展了系统模块的应用。Avalon 外设要么是主外设,要么是从外设。主外设可以于Avalon 上开启总线传输,其至少有一个连接于Avalon 总线模块的主端口。主外设也可以有一个从端口其允许此设备接受其他连接于Avalon 总线的主设备开启的总线传输。而从设备只能响应Avalon 总线传输,而不能够开启总线传输。像存储器,UART 这样的从设备,通常只有与Avalon总线模块相连接的一个从端口。在SOPC 环境中,,区分以下Avalon 总线主设备/从设备的外设类型是十分重要的。

系统模块内部外设

如果SOPC Builder 在外设库中找到了一个外设,或者设计者指定了一个用户外设的设计文件,SOPC Builder 将自动的将此外设与Avalon 总线模块相连接。这种外设是指系统模块之内的外设,也就是被认为是系统模块的一个部分。与Avalon 总线相连接的地址、数据及控制端口是向用户隐藏的。外设中任何附加的非Avalon 端口将作为系统模块的端口显示于外。这些端口可能与物理管脚直接相连或者可能与片上的其他模块相连。

系统模块外部外设

Avalon 总线外设也可以存在于系统模块之外。设计者选择将模块置于系统模块之外可

能有以下几个原因:

■ 外设在物理上位于PLD 器件之外

■ 外设需要某些粘连逻辑(glue logic)使其与Avalon 总线信号连接

■ 在系统模块产生的时候,外设的设计还没有完成

在这些情况下,相应的Avalon 总线模块信号作为系统模块的端口现于外部(及指定的外设)。

主端口(Master Port)

主端口是主外设上用于开启Avalon 总线传输的一系列端口的集合。主端口于Avalon 总线模块直接相连。实际上,一个主外设可能有一个或多个主端口及一个从端口。这些主端口及从端口的相互依赖关系是由对外设进行设计时决定的。但是,这些主、从端口上的单独的总线传输应该总是遵循本文所述。

本文中所提及的所有主设备传输都是指单独的主端口的Avalon 总线传输。

从端口(Slave Port)

从端口是指在位于某一外设上的,从另一外设主端口接受Avalon 总线传输的一系列端口的集合。从端口也直接与Avalon 总线模块相连接。主外设也可以有一个从端口,通过这个从端口可以使其接受Avalon 总线上其他主设备的传输。本文所提及的所有从设备传输都是指单独的从端口的Avalon 总线传输。

主-从端口对(Master-Slave Pair)

“主-从端口对”是指通过Avalon 总线模块相连接的一个主端口和一个从端口构成的组合。从结构上讲,这些主、从端口与Avalon 总线模块上的相应端口相连接。主端口的控制及数据信号可以有效的通过Avalon 总线模块与从端口相互作用。主、从端口之间的连接(这就构成了主-从端口对)是在SOPC Builder 中所确定的。

PTF 文件、SOPC Builder 参数及开关

Avalon 总线及外设的配置可以利用基于向导的SOPC Builder 图形用户接口(GUI)来完成。通过这个GUI,用户可以设定不同的参数和开关,然后据此产生系统的PTF 文件。PTF 文件是一个文本化的文件,它定义了:

■ 定义Avalon 总线模块结构、功能的参数

■ 定义每个外设定义结构、功能的参数

■ 每个外设的主、从角色

■ 外设端口(如读使能、写使能、写数据等)

■ 通往多主端口的从端口的仲裁机制

然后,PTF 文件通过HDL 产生器创建了系统模块的寄存器传输级(RTL)描述。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)