集成电路版图编辑器L-Edit(Layout-Editor)在国内已具有很高的知名度。 Tanner EDA Tools 也是在L-Edit的基础上建立起来的。

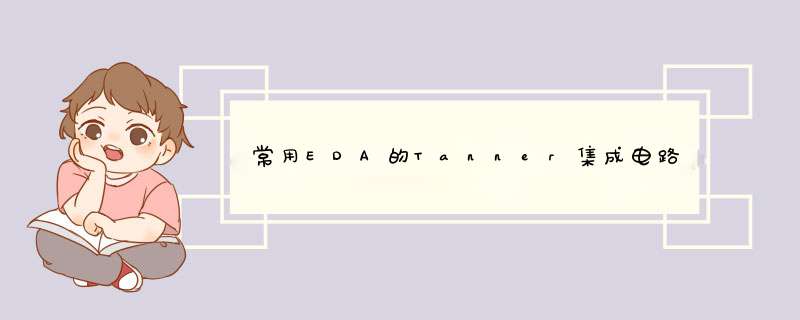

整个设计工具总体上可以归纳为电路设计级和版图设计级两大部分。

即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

电路设计级包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim,以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

版图设计级包括集成电路版图编辑器L-Edit和用于版图检查的网表比较器LVS等模块。

L-Edit本身又嵌入设计规则检查DRC、提供用户二次开发用的编辑界面UPI、标准版图单元库及自动布图布线 SPR、器件剖面观察器 Cross SecTIon Viewer)版图的SPICE网表和版图参数提取器Extract(LPE)等。

网表比较器LVS则用于把由L-Edit生成的版图反向提取的SPC网表和由S-Edit设计的逻辑电路图输出的SPC网表进行比较实现版图检查、对照分析。

L-Edit除了拥有自已的中间图形数据格式(TDB格式)外,还提供了两种最常用的集成电路版图数据传递格式(CIF格式和GDSII格式)的输入、输出功能,可以非常方便地在不同的集成电路设计软件之间交换图形数据文件或把图形数据文件传递给光掩模制造系统。

Tanner集成电路设计中的各种CAD工具

Tanner Pro是一套集成电路设计软件,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS。缺少NetTran和GateSim。

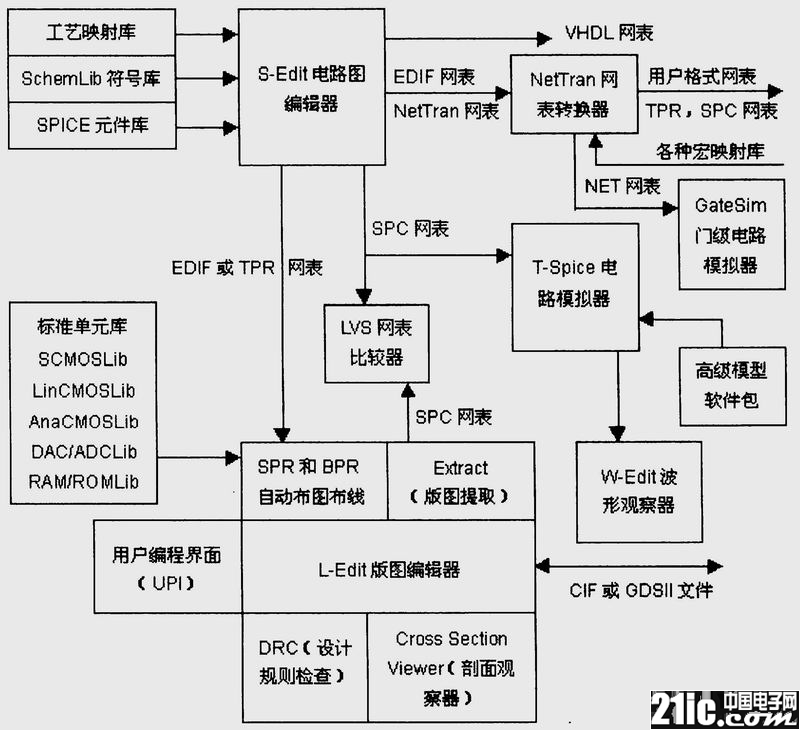

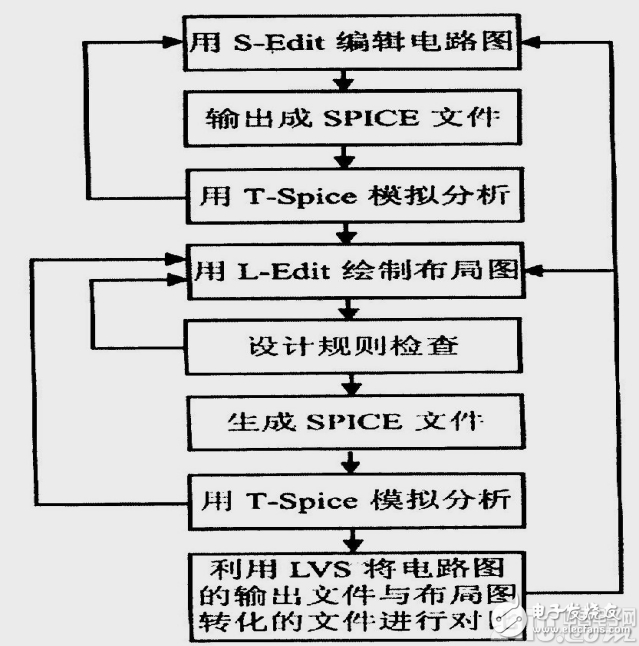

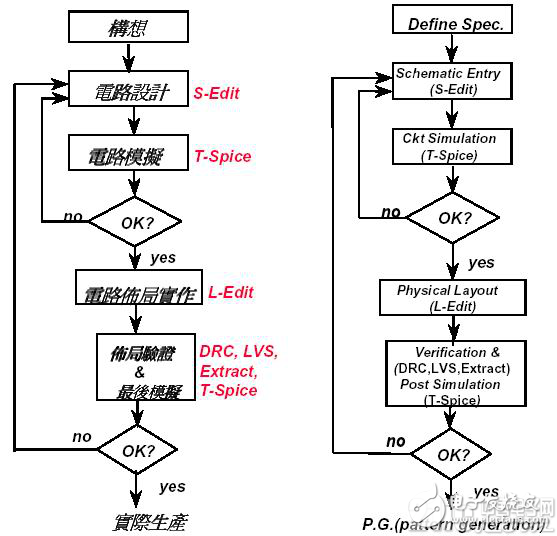

首先用S-Edit编辑要设计电路的电路图,再将该电路图输出成SPICE文件。接着利用T-Spice将电路图模拟并输出成SPICE文件,如果模拟结果有错误,再回S-Edit检查电路图,如果T-Spice模拟结果无误,则以L-Edit进行布局图设计。用L-Edit进行布局图设计后要以DRC功能做设计规则检查,若违反设计规则,再将布局图进行修改直到设计规则检查无误为止。将验证过的布局图转化成SPICE文件,再利用T-Spice模拟,若有错误,再回到L-Edit修改布局图。最后利用LVS将电路图输出的SPICE文件与布局图转化的SPICE文件进行对比,若对比结果不相等,则回去修正L-Edit或S-Edit的图。直到验证无误后,将L-Edit设计好的布局图输出成GDSII文件类型,再交由工厂去制作半导体过程中需要的的光罩。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)