基于BIST的编译码器IP核测

随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设计规模的增大,集成密度的提高,IP引脚的增多,IP的植入深度加大必然使得测试验证工作繁重。据统计,在SOC设计中,各种内核的测试验证工作所用的时间占整个设计过程的60%~80%,SOC及IP核的测试验证已成为SOC技术发展的瓶颈。如何在最短的时间内高效迅速地通过IP核验证与测试.并把其集成在SOC中成为业界关注的焦点和研究领域急待突破与实现的方向。

基于IP核复用的SOC,其IP核类型和来源都不相同,即使已验证好的IP核在集成时也不能确保不出差错。IP核被集成到SOC后,其输入输出端口也嵌入到SOC,原本可测的端口失去了原有的可控性和可观测性,变得不可测。

因此人们一直寻求有效的测试验证技术。本文给出了基于内建自测试方法(BIST),在设计编译码器IP核的同时,考虑其测试外壳设计,以期提高IP核可测性。

2测试结构

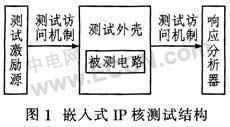

所谓测试,就是在被测电路的输入引脚施加相应的激励信号,然后检测输出引脚的响应,并将检测的输出引脚的响应与期望引脚的响应进行比较以判断电路是否存在故障的过程。

IP核测试的目的在于检测IP核是否存在功能和时序错误,从而对IP核进行修改,提高产品的可靠性。一般采用访问、隔离、控制的手段对IP核的输入端施加激励来得到响应与期望的响应进行比较。嵌入式IP核的测试结构如图1所示。

欢迎分享,转载请注明来源:内存溢出

赞

(0)

打赏

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

“新基建”推动智能楼宇为生命和财产安全保驾护航

上一篇

2022-08-04

清听声学高速公路预警喊话系统助力部署线上线下执法

下一篇

2022-08-04

评论列表(0条)