电子发烧友网:针对目前电子发烧友网举办的“玩转FPGA:iPad2,赛灵思开发板等你拿”,小编在电话回访过程中留意到有很多参赛选手对Xilinx 公司的FPGA及其设计流程不是很熟悉,所以特意在此整理了一些相关知识,希望对大家有所帮助。当然也希望Xilinx FPGA工程师/爱好者能跟我们一起来探讨学习!

需要下载本文的话,请点击以下链接下载:Xilinx FPGA设计实例介绍

一.概述

本文主要帮助大家熟悉利用ISE进行Xilinx 公司FPGA 代码开发的基本流程。主要是帮助初学者了解和初步掌握 ISE 的使用,不需要 FPGA 的开发基础,所以对每个步骤并不进行深入的讨论。

本文介绍的内容从新建 project 一直到下载到硬件观察现象为止,涵盖整个开发过程。考虑到我们的开发一般以 Verilog HDL 或 VHDL 为主,在本文中未介绍原理图输入工具和 IP 核使用工具等。这同时是出于为了使文章脉络更清晰,让大家更快地学会 ISE 的考虑。关于这些专用工具,可以参看 HELP 或者其他文档。

为了更直观的理解,我们需要一个实验平台,在本文中,采用的是 Digital Power Studio 工作组 FPGA SPARK1.1 综合开发平台的 Xilinx 标准型开发系统。如图 1 所示(图中为 Altera 子板,只需改成 Xilinx 的即可)。在该开发系统中,所采用的芯片是SPARTANII系列的XC2S200 。

图1 FPGA SPARK1.1 外观图

二.实现功能

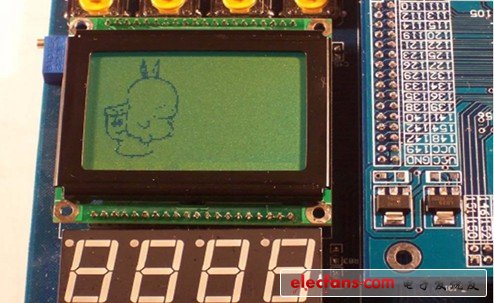

在如上系统中右边有一个 128×64 带背光的点阵型液晶。我们的实验就是用Verilog HDL 编写一段代码驱动液晶显示一个流氓兔。其效果如图 2 所示:

图2 点阵液晶上显示流氓兔的效果图

三.软件准备

本文介绍的是 Xilinx 公司的 ISE 开发环境。现在最新的版本是 ISE7.1,其界与 ISE5.x/ISE6.x 一致。为了更好地进行仿真,还需要安装 Modsim。但是 ISE本身可以进行仿真,也可以不安装 Modsim。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)