关于“进入异常”:在异常发生后,ARM7TDMI内核会作以下工作:

1.在适当的LR中保存下一条指令的地址,当异常入口来自:

ARM状态,那么ARM7TDMI将当前指令地址加4或加8复制(取决于异常的类型)到LR中;

为Thumb状态,那么ARM7TDMI将当前指令地址加4或加8 (取决于异常的类型)复制到LR中;异常处理器程序不必确定状态。

2.将CPSR复制到适当的SPSR中;

3. 将CPSR模式位强制设置为与异常类型相对应的值;

4.强制PC从相关的异常向量处取指。

ARM7TDMI内核在中断异常时置位中断禁止标志,这样可以防止不受控制的异常嵌套。

注:异常总是在ARM状态中进行处理。当处理器处于Thumb状态时发生了异常,在异常向量地址装入PC时,会自动切换到ARM状态。

关于“退出异常”:当异常结束时,异常处理程序必须:

1.将LR中的值减去偏移量后存入PC,偏移量根据异常的类型而有所不同;

2.将SPSR的值复制回CPSR;

3.清零在入口置位的中断禁止标志。

注:恢复CPSR的动作会将T、F和I位自动恢复为异常发生前的值。

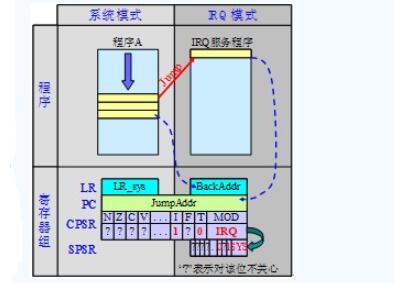

下面利用,图示来演示“进入异常”过程:

1. 程序在系统模式下运行用户程序,假定当前处理器状态为Thumb状态、允许IRQ中断;

2. 用户程序运行时发生IRQ中断,硬件完成以下动作:

(1)将CPSR寄存器内容存入IRQ模式的SPSR寄存器

(2)置位I位(禁止IRQ中断)

(3)清零T位(进入ARM状态)

(4)设置MOD位,切换处理器模式至IRQ模式

(5)将下一条指令的地址存入IRQ模式的LR寄存器

(6)将跳转地址存入PC,实现跳转

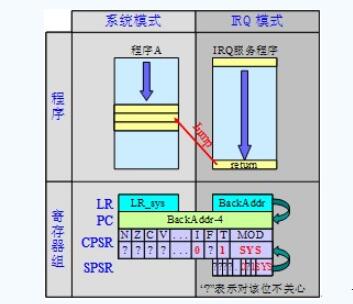

图示“退出异常”过程:

在异常处理结束后,异常处理程序完成以下动作:

(1)将SPSR寄存器的值复制回CPSR寄存器;

(2)将LR寄存的值减去一个常量后复制到PC寄存器,跳转到被中断的用户程序。

下面讲讲“快速中断请求”:快速中断请求(FIQ)适用于对一个突发事件的快速响应,这得益于在ARM状态中,快中断模式有8个专用的寄存器可用来满足寄存器保护的需要(这可以加速上下文切换的速度)。

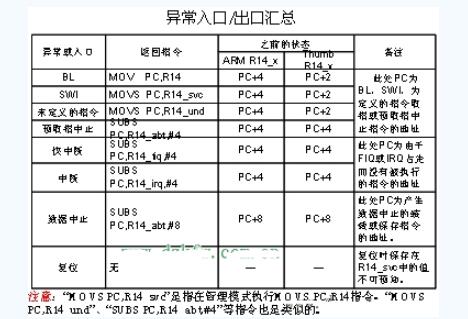

不管异常入口是来自ARM状态还是Thumb状态,FIQ处理程序都会通过执行下面的指令从中断返回: SUBS PC,R14_fiq,#4

在一个特权模式中,可以通过置位CPSR中的F位来禁止FIQ异常。

关于“中断请求”:中断请求(IRQ)异常是一个由nIRQ输入端的低电平所产生的正常中断(在 具体的芯片中,nIRQ由片内外设拉低,nIRQ是内核的一个信号,对用户不可见)。IRQ的优先级 低于FIQ。对于FIQ序列它是被屏蔽的。任何时候在一个特权模式下,都可通过置位CPSR中的I 位来禁止IRQ。

不管异常入口是来自ARM状态还是Thumb状态,FIQ处理程序都会通过执行下面的指令从中断返回: SUBS PC,R14_fiq,#4

关于“中止”:中止发生在对存储器的访问不能完成时,中止包含两种类型:

(1)预取中止:发生在指令预取过程中

(2)数据中止:发生在对数据访问时

中止——预取指中止:当发生预取中止时,ARM7TDMI内核将预取的指令标记为无效,但在指 令到达流水线的执行阶段时才进入异常。如果指令在流水线中因为发生分支而没有被执行,中止将不会发生。在处理中止的原因之后,不管处于哪种处理器 *** 作状态,处理程序都会执行下面的指令恢复PC和CPSR并重试被中止的指令: SUBS PC,R14_abt,#4

中止——数据中止:当发生数据中止后,根据产生数据中止的指令类型作出不同的处理:

(1)数据转移指令(LDR、STR)回写到被修改的基址寄存器。中止处理程序必须注意这一点;

(2)交换指令(SWP)中止好像没有被执行过一样(中止必须发生在SWP指令进行读访问时);

(3)块数据转移指令(LDM,STM)完成。 当回写被设置时,基址寄存器被更新。在指示出现中止后,ARM7TDMI内核防止所有寄存器被覆盖。这意味着ARM7TDMI内核总是会保护被中止的LDM指令中的R15(总是最后一个被转移的寄存器)。

在修复产生中止的原因后,不管处于哪种处理器 *** 作状态,处理程序都必须执行下面的返回指令 : SUBS PC,R14_abt,#8

关于“软件中断指令”:使用软件中断(SWI)指令可以进入管理模式,通常用于请求一个特定的管理函数。SWI处理程序通过执行下面的指令返回: MOVS PC,R14_svc

这个动作恢复了PC和CPSR并返回到SWI之后的指令。SWI处理程序读取 *** 作码以提取SWI函数编号。

关于“未定义的指令”:当ARM7TDMI处理器遇到一条自己和系统内任何协处理器都无法处理的指令时,ARM7TDMI内核执行未定义指令陷阱。软件可使用这一机制通过模拟未定义的协处理器指令来扩展ARM指令集。

注:ARM7TDMI处理器完全遵循ARM结构v4T,可以捕获所有分类未被定义的指令位格式。在模拟处理了失败的指令后,陷阱程序执行下面的指令:MOVS PC,R14_svc

这个动作恢复了PC和CPSR并返回到未定义指令之后的指令。

关于“异常优先级”:当多个异常同时发生时,一个固定的优先级系统决定它们被处理的顺序:

注意:(1)未定义的指令和SWI异常互斥。因为同一条指令不能既是未定义的,又能产生有效的软件中断;

(2)当FIQ使能,并且FIQ和数据中止异常同时发生时,ARM7TDMI内核首先进入数据中止处理程序,然后立即跳转到FIQ向量。在FIQ处理结束后返回到数据中止处理程序。数据中止的优先级必须高于FIQ以确保数据转移错误不会被漏过。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)