随着由电池供电的便携式消费类产品的增长,IC芯片的功耗已成为了一个世界性的问题,设计者必须通过配置合适的功率管理系统采用各种办法来节省能量。便携产品的设计却要求工程师开发更有效的节能系统。随着消费类产品越来越复杂,功率管理系统的设计也越来越复杂。

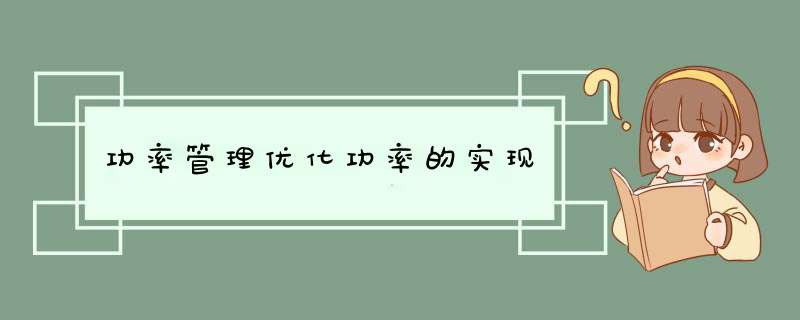

对于移动设备而言,更长的电池使用寿命、更长的通话时间或更长的工作时间都是明显的优势,降低电源要求意味着使用体积更小的电池或选择不同的电池技术,这在一定程度上也缓解了电池发热问题;对于有线系统而言,设计师可通过减小电源体积、减少冷却需求以及降低风扇噪声来提高电池效率。有效的功率管理涉及到恰当技术的选择、优化的库和知识产权(IP)的使用,以及设计方法(图1)。

图1,有效的功率管理需要选择恰当的技术、库和IP设计方案以及芯片设计方法。

功耗在电子设备中正变得更加重要。功率的损耗。电路中通常指元、器件上耗 散的热能。有时也指整机或设备所需的电源功率。 功耗同样是所有的电器设备都有的一个指标,指的是在单位时间中所消耗的能源的数量,单位为W。不过复印机和电灯不同,是不会始终在工作的,在不工作时则处于待机状态,同样也会消耗一定的能量(除非切断电源才会不消耗能量)。

MOS晶体管的基本工作

为了解功率,让我们从经典的MOS晶体管漏极电流方程开始,MOS晶体管是一种新型MOS与双极复合型器件。它采用集成电路工艺,在普通晶闸管结构中制作大量MOS器件,通过MOS器件的通断来控制晶闸管的导通与关断。虽然这些方程只对较老的技术准确,并且未考虑现代技术中的亚微米几何结构引入的各种影响,但它们使人们能了解晶体管的总体行为。

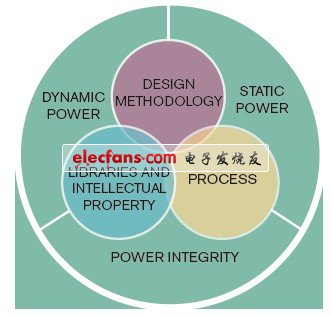

图2,某NMOS FET表明了施加在其端子的电压。

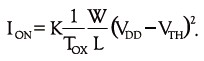

在数字电路中,当晶体管处于接通状态时,它位于饱和区,此时漏极至源极电流IDS服从以下方程(图2):

(1)

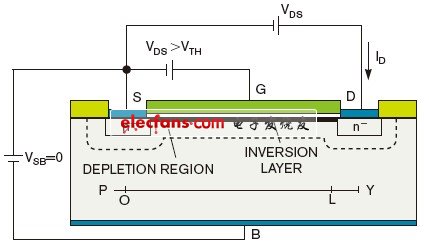

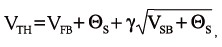

其中TOX是栅极氧化物厚度,W是晶体管的沟道宽度,L是晶体管的沟道长度,VGS是晶体管的栅极与源极之间的电压,VTH是阈值电压,K取决于工艺技术。阈值电压服从以下方程:

(2)

其中VSB是源极与基底之间的反向偏压,VFB是平带电压(它取决于工艺技术),γ和ΘS也是取决于工艺技术的参数。

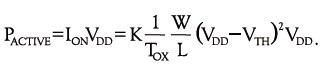

如果漏极至漏极电压等于电源电压,即栅极与源极之间的最大电压,那么你就能运用以下方程来计算接通电流:

(3)

然后可以把有功功率表示为:

(4)

泄漏功率

MOS晶体管中的主要泄漏部分是结泄漏、栅极泄漏、栅极感应漏极泄漏、亚阈值导电。当漏极和基底之间或是源极和基底之间的PN结在晶体管处于关断状态下变成负偏压时,会出现结泄漏,此时由于存在反向偏压二极管而出现泄漏电流。

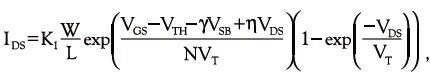

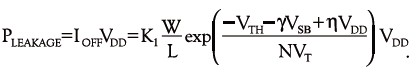

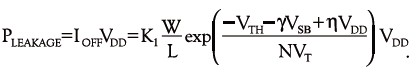

当栅极至漏极重叠区中的高电场导致带至带隧穿,并导致栅极感应漏极泄漏电流时,就会出现栅极感应漏极泄漏。当晶体管处于关断状态时,会出现亚阈值导电;它并非真地处于关断状态,但由于微弱的反相而导电。亚阈值导电是导致泄漏电流的主要因素。你可把该电流表示为:

(5)

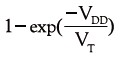

其中K1、γ、η、N取决于工艺,VT是热电压,K1是栅极氧化物厚度的函数。你可以把栅极至源极电压设为0V,并把漏极至源极电压设为等于电源电压VDD,由此获得晶体管中的关断电流或泄漏电流。在这些条件下,由于电源电压远大于热电压,因此你可以把下列项

(6)

近似为1,得出

(7)

现在可把泄漏功率写成

(8)

根据这个结果,你可以看到控制功率的主要参数是阈值电压、氧化物厚度、晶体管长度与宽度、电源电压、反向栅极偏压。由于有功功率随电源电压的平方而变化,因此降低电源电压对降低有功功率具有最大的影响。功率降低速度是电压降低速度的两倍,即电源电压降低20%会导致有功功率降低40%。其余参数只是以线性方式影响有功功率。晶体管长度、宽度或阈值电压的任何明显变化都对晶体管的性能具有不利影响。因此它们在降低有功功率方面仅起着很小的作用。从方程5可看到

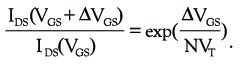

(9)

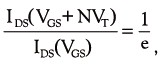

如果ΔVGS = -NVT,则方程变为

(10)

意味着有效栅极至源极电压每降低NVT,N对于某种技术一般是1~2.5,并且阈值电压在室温时等于26 mV,因此栅极至源极电压每变化50 mV~75 mV,你都会看到亚阈值电流降低至2.7分之一。提高阈值电压具有相同效果。因此,阈值电压每提高50 mV~75 mV,泄漏电流都会降低至2.7分之一。阈值电压提高100 mV~150 mV,会使泄漏电流降低至7.4分之一。

你可以通过提高反向栅极偏压来进一步降低泄漏电流。由于存在体偏压系数γ,收效会不太明显。降低电源电压也有助于降低泄漏电流。增加晶体管的沟道长度不仅直接降低泄漏电流(如方程5所示),而且还有助于提高阈值电压(如方程2所示)。

亚阈值电流以指数形式依赖于温度。由于NVT项出现在负指数的分母中,因此在温度升高时,电流会显着增加。这种增加会带来重大挑战,这是因为泄漏功率在高温时变成了总功率的重要部分。

技术的作用

每一次技术进步的目标都是为了改善性能、密度和功耗。工艺设计者调整施加的电压和氧化物厚度来保持相同电场。该途径在每个新的技术节点都会使功率降低大约50%。但是,随着电压的降低,阈值电压也必须降低,来实现该技术的性能目标。

由于无法立即同时在性能和泄漏方面优化某种技术,因此每种技术通常会有两个变种。一个变种针对高性能,另一个针对低泄漏。二者的首要区别是氧化物厚度、电源电压和阈值电压。栅极氧化物较厚的技术变种面向低泄漏设计,并且必须支持更高的电压来实现合理性能。

方程2表明了依赖于工艺的参数γ和ΘS,你可以 *** 纵它们来控制阈值电压。这些参数取决于杂质浓度,工艺设计者可使用一个额外的注入掩模来调节该浓度。然后你可以运用该方法来控制设计方案的泄漏功率。

在选择技术来优化特定设计的功率时,你必须同时考虑两个方面:需要使用更小的几何结构来降低有功功率;需要使用低泄漏的变种来降低泄漏。但在成本和风险方面需要折中。

更小的几何结构需要在掩模成本和其它一次性工程支出方面投入更多的初始资金。虽然它们凭借每块晶圆可生产出更多器件而具有单位成本优势,但它们也在工艺和设计成熟度方面带来了更高风险。如果设计方案包含SERDES等复杂电路,或是该工艺中新出现的其它敏感的块,那么设计风险可能很高。新技术的工艺缺陷通常是在它投产一年或更久之后被全部消除,然后成品率会稳定下来。

问题的答案取决于功率的性质和最终应用。如果最终应用是由电池供电,那么你必须使泄漏最小化。例如,如果你能关断处于待机模式的设计方案,那么它就不需要低泄漏工艺,这是因为你可以关断高性能系统中的电路,并且同时实现低泄漏的好处。

低泄漏工艺需使用更高的电压,并且一般具有更大的面积,因此对于相同性能,会消耗更大的有功功率。因此对于低泄漏工艺选择工作,泄漏功率是首要推动因素。当泄漏功率在设计方案的工作期间成为总功率的重要部分,或是当设计方案对待机模式的功率(泄漏起着主导作用)有严格要求时,选择低泄漏工艺就能满足这些要求。在其它多数情况下,你可以选择标准工艺,用它和多种电路设计方法来优化功率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)