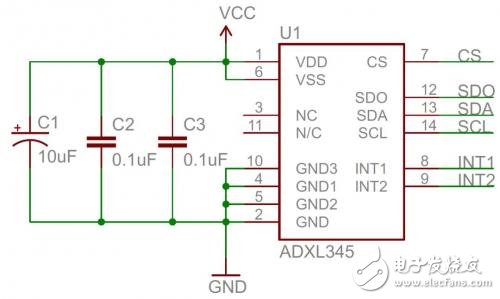

PCB设计过程中工程师几乎必做的事就是给每个电源管脚(Vcc、Vdd等)加上一个0.1uF的陶瓷电容,并在某些地方加上更大容量的极性电容,几乎成了每天吃饭必定要吃碗米一样的事情了,但Why呢?

为什么要加这些电容?

为什么要加0.1uF的?

为什么有时还要加其它值的电容?

在PCB上这些电容放在哪里?

这些我们习以为常的事情细究起来困扰着很多硬件工程师,即便做了很多项目的老司机也未必能给你讲清楚这里面的关系,不信你问问你们实验室的大哥?

还有一个让很多人抓狂的问题 - Decoupling Cap(去耦电容)和Bypass Cap(旁路电容)的区别,看到很多文章的作者把这俩概念的区别讲得貌似斩钉截铁,但读下来却发现其实作者也并不真正清楚,当然也不排除我自己的阅读能力出现了问题,不信你从网上搜几篇文章读读,越发的糊涂。

作为一个实用主义者,我从来不在乎概念如何叫,只是从功能上来理解为什么。

很多文章都从晶体管级别深入分析了为什么要加去偶电容,既有图又有公式,貌似揭示了真相,但这些分析看半天你未必看懂,看懂了未必能记住,苏老师今天不讲高深的理论,从宏观上让大家清楚为什么就可以了。

本质上我们设计的所有电路可以像下图一样抽象一下:

板子上有n个不同的负载(比如某个运放电路、MCU的内核、MCU的IO、ADC、时钟),每个负载都需要稳定地供电 - 电压稳定、干净,电流充足,在此图上我只画出2个负载进行举例;

电源产生电路,它为每个负载提供能源

每个负载要正常工作,前提就是负载上的供电电压要稳,如果是5V,就得是尽可能干净的5V,如下图:

(手画的,有点不平,意思到了)

但该负载内的器件们工作起来,都要动态地吸收电流,供电电压就变成了下面的鸟样子:

也就是在5V的DC上叠加了各种高频率的噪声,这些噪声是由于器件对供电电流的需求导致的电压波动,可以看成是在DC 5V上“耦和”了由于器件工作带来的AC噪声。

这样耦和了AC的DC供电电压不仅会影响本负载区域内的电路的工作,也会影响到其它连接在同一个VCC上的其它负载的工作,有可能导致那些负载的电路工作出现问题。

怎么办呢?当然就是把每个地区的问题控制在该地区范围内喽:

电源供电取决于变换的方式,其供电本身在DC上就有纹波,因此我们需要在电源输出Vout端要有电容C1(我们可以看成是国家粮仓)负责将供电电压上的噪声降到尽可能的低,完全为零是不可能的,因为完美的世界从来都不存在,只要不影响后面负载的正常工作即可。

既然每个负载工作起来会导致其电源出现额外的波动,那就让波动在本地尽可能降低,且不影响到其它负载的工作。降低负载供应波动影响的方式就是加强能即时响应的供给(本地粮库) - 通过备用的供给平滑掉主供给快速反应方面的不足。电容的本性就是储能,用电容来做备用电能提供供给也就能平滑掉负载瞬间的需求带来的波动(不同的电容响应速度也不同,且听下文分解),保证该负载的电压尽可能稳定,也就是将有可能耦和到DC上的AC给去除掉(去耦的含义1),同时由于让本地的DC稳定,降低了对其它负载的波及(去耦的含义2)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)