引言

目前的有源电力滤波器通常是采用基于瞬时无功功率理论的谐波电流检测方法。其中的ip-iq算法需要用到与电网电压同步的正余弦信号,即与电网电压同频同相的标准正余弦信号。该信号的获取可以采用锁相环加正余弦函数发生器的方法,也可采用软件查表的方法。本设计采用全硬件电路完成,即通过锁相环加正弦函数发生器的方法,可自动实时跟踪电网电压的频率和相位,不占用微处理器的软、硬件资源,大大降低了谐波检测算法编程的复杂度。

电路原理

此电路从原理上可分成电网电压取样、正弦波/方波转换、鉴相、低通滤波、电平转换和正弦波产生几个部分。其基本原理是利用电压互感器对电网电压进行取样,然后经过过零比较器,得到一个与电网电压同步的方波信号,作为鉴相器(PD)的一个输入。鉴相器、低通滤波和函数发生器ICL8038组成一个锁相环(PLL)电路。当环路锁定时,输出正弦波与电网电压同步,即同频同相,在时间上应该几乎没有延迟。原理结构图如图1所示。

图1 与电网电压同步的正弦波发生电路原理结构图

正弦波/方波转换电路

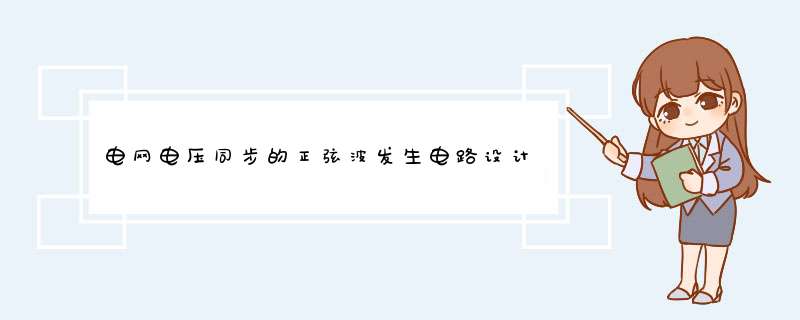

利用电压互感器对电网电压进行取样,然后经过过零比较器,得到一个与电网电压同步的方波信号。电路如图2所示。

图2 正弦波/方波转换电路

鉴相与低通滤波电路

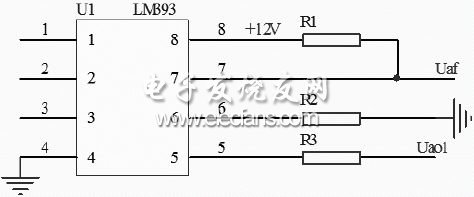

本设计中的鉴相器使用CD4046的PD1。PD1由异或门构成,要求输入波形的占空比基本上是50%。与PD2(上升沿触发工作)相比较,由于PD1是电平触发工作,输入波形中即时叠加有噪声,对PLL稳定工作的影响也较小,具有较强的抗噪声能力。电阻R4和电容C1构成低通滤波器。电路如图3所示。

图3 鉴相和低通滤波电路

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)