用 FPGA 嵌入式处理器实现您的构想

在采用数值处理技术创建嵌入式应用时,通常以整数或定点表示法来确保算术运算尽量简单,这一点至关重要。因其不仅有助于使成本和功耗降至最低,而且还能尽可能地加速硬件部署。

FPGA 非常适用于执行定点运算,并能在逻辑或基于软件或硬件处理器的实施方案中创建高度并行的数据路径解决方案。Virtex®-5 FPGA 产品系列中 FXT 系列的最新硬件处理器 Xilinx® PowerPC® 440 可提供超标量功能,让用户能够对器件编程,使其以高达 550 MHz 的时钟速率并行执行一个或两个定点运算。

尽管用户能通过对器件进行编程来执行大多数采用整数或定点算术的运算,但通常须重新运算并插入比例运算以确保计算结果足够精确。对于复杂运算而言,这不仅耗时,而且还会导致程序变为专用型且不可重用。理想的替代方法是采用标准浮点表示法来提供一种适用于多个应用的高动态范围。这样人们就无需修改算法即可获得适用于任何特定应用或 *** 作环境的定点实施方案,也无需为随后的项目及应用而大范围地修改代码。

虽然赛灵思为基于 IBM 浮点性能库的 PowerPC 440 处理器提供了一种行之有效的仿真浮点解决方案,但处理器内核仍需占用数十个周期来执行每条运算。而采用浮点运算单元 (FPU) 形式的浮点运算硬件加速功能可缩短该运算周期。Virtex-5 FXT 系列中的 PowerPC 440 处理器提供了有效接口,能够将赛灵思软 FPU 等硬件加速连接至该处理器内核。该方案可通过结构协处理器总线 (FCB) 将 PowerPC 440 处理器上的 128 位辅助处理器单元 (APU) 接口桥接至协处理器。使用该类协处理器(赛灵思 LogiCORE™ IP Virtex-5 APU-FPU),Virtex-5 FXT 用户可以选择软件仿真或者专用软逻辑 FPU 在 PowerPC 上自如地实现浮点运算。图 1 显示了通过 FCB 将 PowerPC 440 处理器连接至 Virtex-5 APU-FPU 的典型实施方案。

图 1——包含 APU-FPU 内核的嵌入式处理器系统

PowerPC 440 Processor Block: PowerPC 440 处理器模块

PowerPC 440 Processor: PowerPC 440处理器

PLB and Memory Crossbar: PLB 和存储器交叉开关

Virtex-5 APU FloaTIng-Point Unit: Virtex-5 APU 浮点单元

in FPGA Logic: FPGA 逻辑内

关于 PowerPC 440 FPU

赛灵思针对嵌入在 Virtex-5 FXT FPGA 中的 PowerPC 440 处理器专门设计了 APU-FPU。FPU 通过 APU 接口与处理器的紧密结合可让浮点运算单元直接执行原生 PowerPC 浮点指令,这相对软件仿真而言,速度一般可提高 6 倍。

除少数情况外,赛灵思 PowerPC FPU 一般符合单精度和双精度浮点运算的 IEEE-754 标准。赛灵思提供了为 2:1和 3:1 APU-FPU 时钟速率而优化的变量,使 PowerPC 处理器能够以最高频率运行。自发性指令发送不仅会隐藏运算时延,而且还会减少每条指令的周期。此外,这些优化的实施方案可充分发挥器件的高性能 DSP 特性,以缩短运算符时延并减少逻辑计数与功耗。赛灵思在其嵌入式开发套件 (EDK) 中支持 APU-FPU 流。

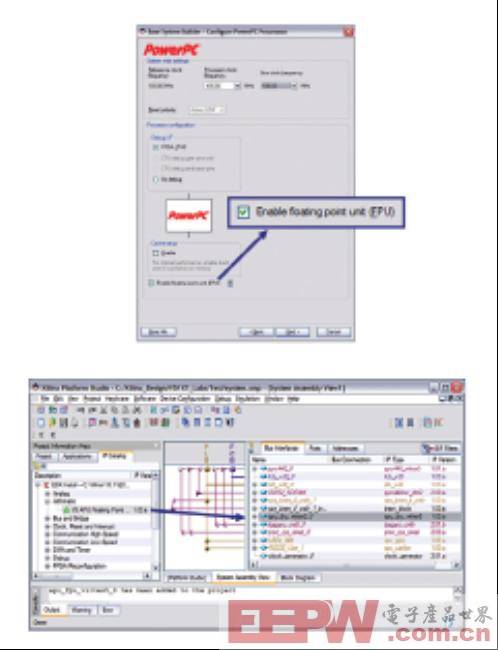

图 2 为 FPU 架构的整体框架图。APU-FPU 由执行单元、寄存器文件、总线接口以及所有管理浮点指令执行情况所必需的控制逻辑组成。

FCB2 Bus: FCB2 总线

FCB2 Bus Interface: FCB2 总线接口

ExecuTIon Control/Decode Logic: 执行控制/解码逻辑

Register File & Forwarding: 寄存器文件与转发

Add/Sub/Convert: 添加/子集/转换

Compare: 比较

MulTIply: 乘

Divide: 除

Square Root: 平方根

Round: 四舍五入

图 2——Virtex-5 FXT PowerPC 440 浮点协处理器架构

FPU 含有两个变量。双精度变量可执行除 PowerPC ISA 图形子集(fsel、fres 和 frsqrte)以外的所有浮点指令,其中也包括单精度变量执行的指令。这意味着您能使用带各种商用编译器和 *** 作系统的 FPU

赛灵思编译器支持的 APU-FPU 单精度变量使用的资源较少。当 FPU 被占用时,双精度 *** 作将通过软件仿真来执行。

软 FPU 比软件仿真法平均快 6 倍。单精度 FPU 通常比双精度快 13%

将 APU-FPU 连接至 PowerPC 440

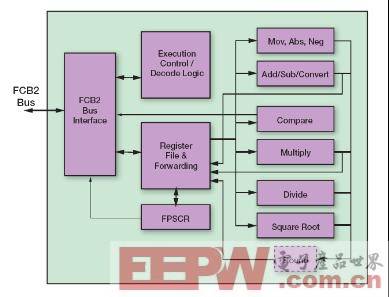

有两种方法可将 APU-FPU 连接至 PowerPC 440 处理器:1、利用赛灵思 Platform Studio 设计工具中的 Base System Builder (BSB) 向导;2、将 APU-FPU 单元添加至当前设计方案中即可。

您首先需利用 BSB 向导确定目标板和所期望的处理器(PowerPC 或 MicroBlaze™),然后通过一系列复选框和下拉菜单选择设计中所需的 IP。借助 BSB 向导,能够轻松快速地组装并测试基础处理器系统。您只需勾选您要选择的 FPU 框,即可实现APU-FPU 连接(见图 3 顶部)。该向导可实现一个经过优化能以处理器时钟三分之一速率运行的双精度 FPU。您也可定制更高时钟速率的 FPU 和单精度 FPU。

如果不想使用向导,您也可通过另一种方法来实现,即按照系统组装视图拖动 IP Catalog 下的 APU- FPU IP,然后对 FPU 进行配置即可。图 3 底部图片显示了 IP Catalog (见左下方)和系统组装视图中新添加的 FPU。右击 FPU 并选择 Configure IP,然后您便可选取想要的精度(单精度或双精度)并确定您希望该 FPU 是针对低时延(三分之一时钟速率)或是高速率(二分之一时钟速率)而进行优化;最后将 FPU 连接至 FCB 并将 FPU/FCB 时钟链接至适当的时钟(通常是二分之一或三分之一处理器时钟速率。)

图 3——通过 BSB 向导(顶部)以及系统组装视图将 FPU 添加至现有 PowerPC 处理器设计方案中

让浮点尽在掌握之中

Virtex-5 APU-FPU 提供免费的 Platform Studio,支持浮点定制。您可分别采用约 2500 个或约 4900 个 LUT 寄存器对来实现单或双精度 FPU,也可在无需添加 FPGA 逻辑的情况下运行具有浮点仿真功能的软件应用。

性能水平可预先选择:选择适当的 FPU,或实施设计并确定软件仿真是否满足要求;如未满足,可升级软 FPU。

显而易见,如果能从软件仿真中获得足够的性能,则无需 FPU。但如果需要更高的性能,可使用 APU-FPU。如果应用需要 FPU 或正在使用与之配套的编译器,可选择双精度 FPU。如果应用仅需单精度运算且您正在使用赛灵思 GNU 编译器,则单精度 FPU 会降低逻辑要求。谨记,如果选择双精度 FPU,它将执行单精度运算,然后将运算结果进行四舍五入,以提供单精度 FPU 的精确度。

典型性能增益

当您在评估是需要硬 FPU 还是软 FPU 时,应首先确定代码的浮点密集程度。代码通常包括不同浮点、整数、存储器以及逻辑运算等。因此,尽管基准可作为潜在性能提升的指示器,但运行您自己的代码会更好。

表 1 列出了 400 MHz Virtex-5 FXT PowerPC 440 处理器、软件仿真以及与该处理器相连的 200 MHz 双精度 APU-FPU 的基准数据,透过该表可清晰了解 APU-FPU 执行浮点密集代代码的性能表现。

表中所列数据是赛灵思用于评估处理器浮点单元性能的一组基准数据的子集。平均而言,软 FPU 可比软件仿真快 6 倍,而单精度 FPU 可比双精度 FPU 快 13%。

在浮点占主导地位的情况下,可通过优化代码来提高软 FPU 的性能,以充分利用 FPU 管线。FIR 滤波器基准就是一例很好的潜在性能增益。未经优化的代码是典型的“教科书代码”,虽便于阅读,但大多数 FPU 执行时往往效率低下。然而,通过实施循环展开、最大限度地延长 FPU 寄存器中常数的保留时间,以及交叉存取其他代码与浮点指令,设计方案的性能可得到显著提高。在本例中,优化滤波器代码比未经优化的代码快 3.8 倍,比软件仿真快 30 倍。

总之,Virtex-5 FXT 借助其 PowerPC 440 处理器可为嵌入式应用提供众多选择。您可在有无 FPU 的情况下执行设计方案、用性能较高的 FPU来替代软件仿真技术、为 Virtex-5 FXT 量身定制处理能力资源,所有这些都是为了满足您的最佳设计需求,让“一切尽在您的掌握之中” 。

* EDK 10.1 SP2 GNU 带标志的编译器:-O3 -funroll-循环

表 1——400 MHz 处理器与 200-MHz FPU 的典型浮点性能

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)