1.设计摘要

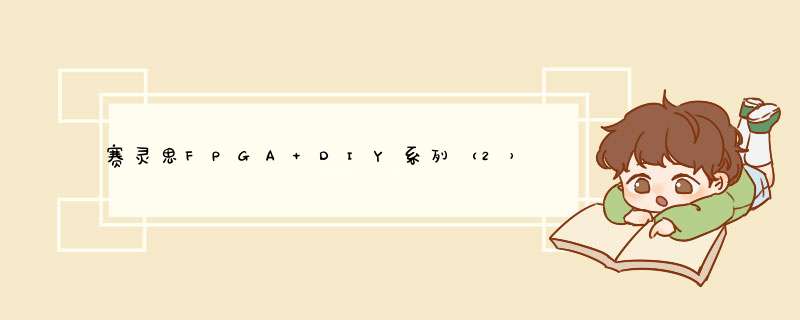

频率特征测试仪是用来测量电路传输特性和阻抗特性的仪器,简称扫频仪。扫频信号源是扫频仪的主要功能部件,作用是产生测量用的正弦扫频信号,其扫频范围可调,输出信号幅度等幅。本设计采用DDS(数字频率合成技术)产生扫频信号,以Xilinx FPGA为控制核心,通过A/D和D/A等接口电路,实现扫频信号频率的步进调整、幅度与相位的测量,创新的使用了计算机软件作为仪器面板来显示被测网络幅频特性与相频特性,并且测试结果可保存到各种存储介质中。

2.适用范围以及针对用户群

作为一种仪器可以用于各种实验教学及科研场合。

图1 整体设计框图

3.具体功能模块

3.1 DDS扫频信号产生模块

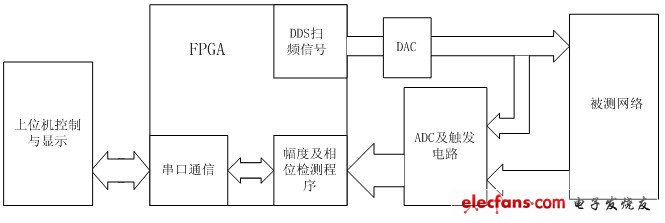

直接数字频率合成技术(Direct Digital Frequency Synthesis简称DDS)是一种全数字技术,与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

DDS的基本原理是:相位累加器对频率控制字进行累加,利用相位累加寄存器的值对存储正弦波形的查找表进行寻址,使之输出相应的幅值码,幅值码再经过数模转换器DAC得到相应的阶梯波,最后使用椭圆低通滤波器对其平滑得到所需的连续波形频率信号。

图2 DDS原理图

3.2 被测系统参数测量模块

1)幅频特性测量:扫频信号输出幅值是确定的,只需测出被测系统输出信号的幅度,即可算得其增益。测量输出幅值使用A/D转换器及外围检测电路实现。

2)相频特性测量:扫频信号和被测系统输出信号经过触发电路变换为矩形波,送入测相逻辑电路中。测相逻辑电路由参考时钟对相位差进行计数测量,从而得到两者的相位差值。

3.3 上位机软件设计部分

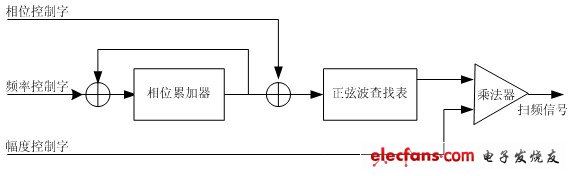

我们使用VB进行软件编程,通过MSComm控件进行串口通信,控制系统的工作状态和波形数据的显示。通过软件设置可以控制扫频信号的起始频率和终止频率。显示时可以直接显示和对数显示,并可以通过文件的方式将波形数据保存下来。软件界面如图所示:

图3 上位机软件界面

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)