近年来,因数字化产品对高分辨率A/D,D/A转换器需求的激增而得到广泛地应用。Delta-Sigma A/D转换器的构想出现已有很多年了,早期因受集成电路制造技术的限制,未在产品中广泛使用,随着集成电路制造成本不断降低,该技术的应用渐多,目前已成为高精度ADC的主流技术。随着该技术的趋热,有更多人想了解其工作原理,但目前国内的教材对其涉及还不多,期刊论文多侧重数学演绎,文献中未见有详尽的仿真实例。

除了制造专用ADC,该技术还易于用FPGA实现,逻辑电路可以完全集成在FPGA内部,只需要很少的外围元件,就可以用FPGA直接进行混合信号处理。由于FPGA可扩展和可重配置的特性,特别适合产品研发和小规模生产的场合,另外用FPGA在单一芯片上实现多路Sigma-Delta A /D转换也很容易。

Delta-Sigma有时称其为Sigma-Delta,或∑-△。

1 Delta-Sigma A/D转换器原理

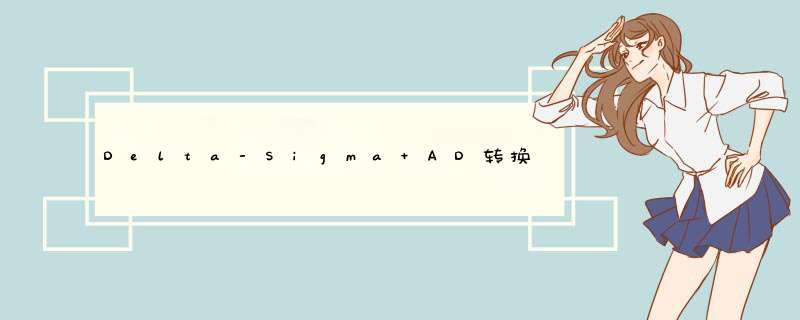

在△-∑A/D转换器中,模拟输入电压信号被连接到一个积分器的输入端。在输出端对应输入大小产生一个电压变化率,或者斜坡。然后用比较器将该斜坡电压与地电位(0V)进行比较。比较器的行为就像1位A/D转换器,根据积分器的输出是正或负产生1位的输出(“高”或“低”)。比较器的输出通过一个以很高频率时钟驱动的D触发器被锁存,并且反馈到积分器的另一个输入通道,向0V方向趋势驱动积分器。基本电路如图1所示。

在图1中,最左边的运放是积分器。积分器馈入的下一个运放是比较器,或1位A/D转换器。接下来是D触发器,在每个时钟脉冲锁存比较器的输出,发送“高”或“低”信号到电路顶部的下一个比较器。最后这个比较器用于转换信号极性,将触发器的0 V/5 V逻辑电平输出转换到V+/V-电压信号再反馈到积分器。

如果积分器输出是正,第一次比较器将输出一个“高”信号给触发器的D输入。在下一个时钟脉冲,“高”信号将从Q线输出到最后一个比较器的放大器输入。最上面的那个比较器将看见一个输入电压大于+1/2 V的阈值电压,它向正方向饱和,发送一个满V+信号到积分器的另一个输入端。这个V+反馈信号向负方向驱动积分器输出。如果输出电压一直为负,反馈环将发送一个矫正信号(V-)回到积分器的顶部输入,向正方向驱动它。这就是△-∑行为的概念:第一个比较器感知在积分器输出和0 V电压之间的差(△),积分器求模拟输入信号与最上面比较器输出的和(∑)。

2 PSpice仿真

通过PSpice仿真模拟实验,可以更容易和更清楚地理解△-∑A/D转换器的工作原理。下面采用PSpiee仿真△-∑A/D转换器。本文使用CaptLire CIS Lite EdiTIon 9.2绘制电路图,用PSpice Lite Version 9.2进行仿真。

2.1 绘制电路图

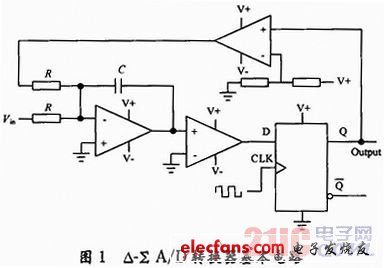

先用OrCAD Capture绘制△-∑A/D转换器电路图,如图2所示。信号源采用FREQ=100 kHz的正弦信号。偏移VOFF=0,幅度先设置为0 V,AMPL=0。

为方便起见图中所有的运算放大器都使用uA741模型,因为这个模型很容易找到,实际项目中根据需要选用合适的运放。D触发器使用74LS74。在CaptureCIS Lite EdiTIon 9.2和PSpice Lite Version 9.2中没有74LS系列的元件符号库74ls.olb也没有仿真库74ls.lib,可以从下面的网站下载:

http://power.teipat. gr/download/OrCAD/OrCAD%20Libraries/Library%20for%20Capture/PSPICE/

74LS系列是低功耗肖特基型TTL器件,输入高电平最小为2.0 V,输入低电平最大为0.8 V;输出高电平最小位2.7 V,输出低电平最大为0.5 V。采用R3和R4分压将U2的输出电压转换为0~3.75 V电压,以适应TTL输入电平。74LS模型只接受正电压作为电平信号,所以可以不理会比较器U2的负电压输出。R6和R7分压15 V为2.5 V作为参考电压,将74LS74的TTL输出电平通过U3转换为V+/V-的电压信号。D触发器的时钟由DSTM1提供。从74LS74的产品手册可知,当LCR和PRE端都为高电平时,在时钟的上升沿,D触发器将输入端D的数据送到输出端Q,并锁存到下一个时钟的上升沿。这个高电平由DSTM2提供。图3是在STImulus Editor中显示的STM1和STM2的波形,双击波形可以对它进行编辑。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)