频率是电信号中重要的物理量,在电子、通信系统中,信号的频率稳定度决定了整个系统的性能,准确测量信号的频率是系统设计的重要内容。

单片机广泛地应用于电子系统设计,其性价比高,大量的外围接口电路,使基于单片机的电子系统设计方便,周期缩短。然而,单片机的串行工作特点决定了它的低速性和程序跑飞,另外还存在抗干扰能力不强等缺点。EDA(Electronic Design AutomaTIon)技术以计算机为工具,在Quartus II软件平台上,对以硬件描述语言Verilog HDL/VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、综合及优化、逻辑仿真,直至对特定目标芯片的适配、编译、逻辑映射和编程下载等工作,FPGA是纯硬件结构,具有较强的抗干扰能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法,实现了频率的自动测量,测量范围为0.1 Hz~50 MHz,测量误差小于0.01%。

1 8051IP(Intelligent Property)软核

8051单片机是以由VQM原码(Verilog Quartus Mapping File)表达的,在QuartusII环境下能与VHDL、Verilog HDL等其他硬件描述语言混合编译综合,并在单片FPGA中实现全部硬件系统。

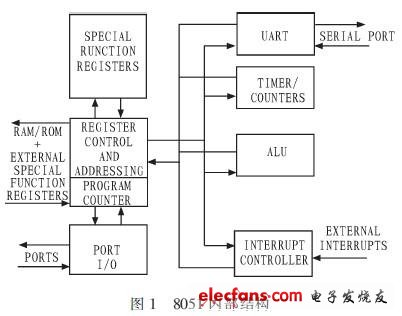

MC8051单片机核含有8位复杂指令CPU,存储器采用哈佛结构,其结构框图如图1所示。

MC8051的指令系统与8051/2、8031/2等完全兼容,硬件部分也基本相同,例如可接64KB外部存储器,可接256字节内部数据RAM,含两个16位定时/计数器,全双工串口,含节省功耗工作模式,中断响应结构等。不同之处主要有:

1)MC8051是以网表文件的方式存在的,只有通过编译综合,并载入FPGA中才以硬件的方式工作,而普通8051总是以硬件方式存在的;

2)MC8051无内部ROM和RAM,所有程序ROM和内部RAM都必须外接。

3)以软核方式存在能进行硬件修改和编辑;能对其进行仿真和嵌入式逻辑分析仪实现实时时序测试;能根据设计者的意愿将CPU、RAM、ROM、硬件功能模块和接口模块等实现于同一片FPGA中(即SOC)。

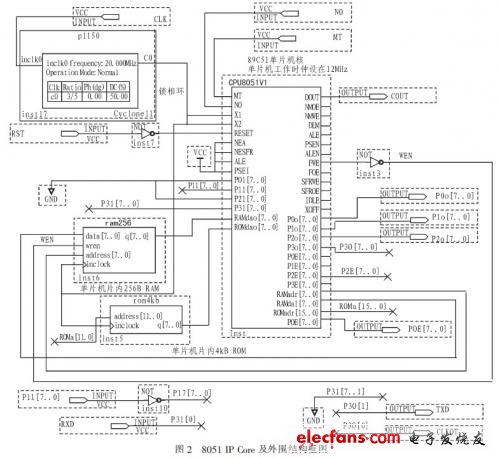

MC8051核在接上了ROM和RAM后就成为一个完整的8051或8052单片机了,MC8051核实用系统的最基本构建顶层原理图如图2所示,主要由4个部件构成。

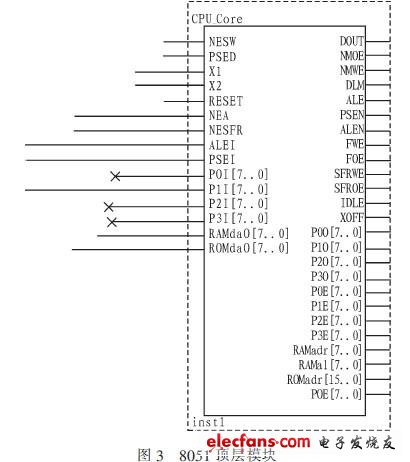

1)MC8051核。CPU_Core即MC8051单片机核如图3所示,由VQM原码表述:CPU_Core.vqm,可以直接凋用。该元件可以与其他不同语言表述的元件一同综合与编译。

2)嵌入式锁相环PLL50。其输入频率设置为50 MHz,MC8051能接受的工作时钟频率上限取决于FPCA的速度级别。

3)程序ROM,LPM_ROM。采用ROM容量的大小也取决于FPGA所含的嵌入RAM的大小。设置的ROM容量是4k字节。此ROM可以加载HEX格式文件作为单片机的程序代码。HEX程序代码可以直接使用普通8051单片机程序编译器生成。

4)数据RAM,LPM_RAM。本系统设置的LPM_RAM容量是256字节。高128字节须用间接寻址方式访问。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)