本章节列举了DAC/比较器架构和集成ADC相比所具备的优势。所讨论的应用电路既常见又简单,也存在一些共性问题。

首先,考虑采用低成本方法实现电力线电压跌落、浪涌以及瞬态检测和故障记录。理想的设计是采用墙上设备监测电力线异常,并将每次异常发生的时间记录到RAM中(电压跌落和浪涌的持续时间可以从几毫秒到几小时;瞬态可能短至10微秒)。监视器必须记录电力线完全失效的持续时间,因此,监视器应当由电池供电。

传统解决方案是采用控制器和ADC。由于转换器连续对电力线电压采样,控制器需将每次采样值与软件中用户设定的限制进行比较,并将任何超出规定的状态记录到RAM。由于系统必须能够追踪到短至10µs的瞬态情况,ADC采样间隔必须相当短——保守估算时间可以长达2.5µs。因此,控制器必须以1/2.5µs = 400ksps的速率进行采样处理。

如果软件比较具有高效编码并且ADC无需处理器干预,系统每次采样可执行少于10条指令,这就要求处理器具有4MIPS的能力。这种执行能力并不适合采用电池供电(图1)。需要考虑用模拟方法对输入瞬态偏离进行响应,用以替代连续跟踪方案。

在这种情况下,DAC/比较器替代方案提供了几个明显优势。需要4个DAC和4个比较器(或一片MAX516),后面连接一个4路设置/复位触发器。一组DAC/比较器/FF监测高瞬态电压,一组监测低瞬态电压,一组用于监测电网跌落,一组用于监测浪涌(图2)。瞬态电压直接耦合到比较器,连接到电压跌落和浪涌监测比较器的输入首先要进行整流和滤波,以获得电网电压的平均值。可在软件中调整到合适的rms。

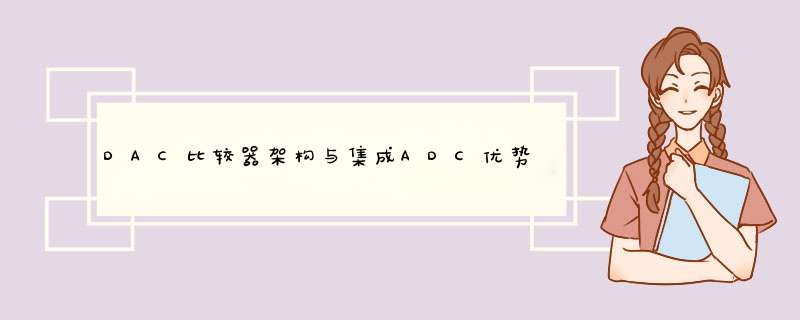

系统每T秒进行采样并对触发器复位,此处T为瞬态记录时间分辨率(也许为60s)。高、低瞬态电平DAC用于设置所要求的门限。电压跌落和浪涌DAC在每T秒间隔后进行调整,采用逐次逼近技术产生高、低门限,以跟踪目前平均值。

假设执行逐次逼近以及其它任务的子程序具有1000条指令(保守估计),对于T=60s,CPU平均每秒执行17条指令。执行速率是0.00002MIPS,非常适合低功耗系统,远远低于ADC方案的4MIPS。为进一步降低功耗,控制器可在大部分时间内处于“休眠”,仅在处理电力线异常时唤醒。将电压比较从软件方式转换为模拟硬件方式,该电路大大降低了功耗、设计复杂性以及成本。

较低的故障检测和诊断维护成本

打印头控制、车辆控制以及许多其它机电应用,需严格监视内部电压和温度以确定何时更换工作模式。极端情况下,这种反馈可使系统避免全部关断自毁。例如,在必要时步进电机控制器必须调整输出MOSFET的栅极驱动以避免线性工作时消耗过多功率。

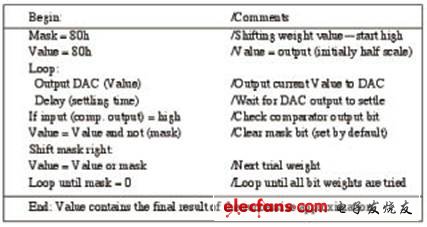

监测这些问题的传统方法是采用ADC(图8a)。处理器控制ADC进行周期性测量,与控制处理保持时间常数一致。然后对结果的量化值进行缩放后与软件中的门限进行比较。如果超出范围,可触发纠正动作或者全部关断系统。

另外一种方法是采用DAC/比较器组合(图8b)。静态DAC输出建立关断门限或比较器触发值。当温度变化造成比较器触发,比较器会对处理器发出中断来启动纠正动作。必要时,处理器还可以通过启动基于软件的逐次逼近程序来确定极限温度值。

表1 逐次逼近伪代码

图8 在这种情况下,用DAC和比较器(b)替换ADC(a)可降低系统成本、响应时间以及软件开销

另一方面,为支持ADC,处理器在跳转到关断子程序之前必须轮询ADC、输入采样值并与先前设定值进行比较。这样,DAC/比较器不仅节约成本,而且提供了比采用ADC的更快响应;同时还减小了处理器开销。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)