一、您好:我看到很多SDRAM的数据、地址总线上都串接了小电阻(10欧姆到100欧姆);

1、这样做的主要目的是什么?串接的电阻阻值应该怎么来确定?

2、对于程序FLASH(比如NOR型的flash,access TIme=70ns)的数据和地址总线需要这样做吗?

不知道你的具体的拓扑结构,我觉得主要是限制信号的反射和过冲的。这要根据你的拓扑结构以及芯片的驱动能力及时序要求决定。

二、是TR or TF决定该线路是否为高速信号,在信号的测量中,我们经常会发现信号的上升沿太缓慢,或出现抖动,那么他究竟有什么因素决定呢? 与逻辑们本身的性能和负载大小有什么具体的关系,以前在作阻抗匹配的时候会发现加大了窜连珠智慧会增大TR.

决定因素很多,例如你的负载是否太重,你的匹配是否合适,芯片的驱动能力等等。这个要分DC和AC来分析,我们在设计时主要看AC,驱动外的负载在芯片Switch时,可等效为阻容电路,实际就是驱动芯片对这个阻容的充放电能力。 加大串连电阻的阻值,RC电路的时间常数显然会增加,你的上升下降沿自然会变缓。

三、在做AGND和DGND的分割时,隔离槽的宽度多少为合适?8mil是否足够(fallTIme=3ns)?

如果是Agnd和Dgnd的话,主要是看EMC的要求和加工的要求(防止短路),我们一般是50mil,8mil可能太小。 Dear sir,

四、Could you tell me how to idenTIfy the reasons that cause SI problems from the waveforms of a signal? For example: it‘s cause by unmarched impadance, ect.

Thank you!

It’s difficult to idenTIfy the exact reasons just from the waveforms of a signal. Because the waveform is the total effect of all SI causes(noise)。 So you can just find the possible problems in your real design. Of course, if you just change one parameter(eg. termination resistor) you can get some rules of waveform. You can do some sweep simulation in some simulators to get some results.

五、我们在设计PCB时,将CPU的16位数据和24位地址总线用一个扩展接口引出,以期望能扩展多个其它外部设备。总线频率最高可达40MHz。我们希望使用比较通用的连接器,因此打算采用PC104模块上所使用的64pin长引脚连接器,引脚数量和扩展功能都能满足。

请问专家:采用此连接器是否会制约总线的频率?

采用连接器肯定会对这些信号的质量有影响,但是否制约总线频率,就要看设计的好坏了。在设计时,要考虑串扰,反射、以及时序,对于连接器来说,就需要很好的安排信号在连接器上的分布,以及两边PCB的走线。

六、有几个名词的定义我不是很清楚,就是:

1、什么叫微带线、带状线?

2、什么叫电长走线?

1 在PCB上,微带线一般是指传输线只有一个参考平面的传输线,一般就是表层的走线;带状线一般是指在传输线的两侧都有参考平面的传输线。

2 我也没听说过“电长走线”。

七、如果给一个SDRAM(rise time=0.2ns)走数据总线,走线宽度6mil;过孔尺寸:外18mil,内10mil;走线长度为1.2英寸;

在上述情况下,您认为最佳的过孔数量应该是多少?计算的主要依据是什么?

过孔的影响主要是两方面:一是影响信号质量;二是影响信号的时序。这两方面是互相影响的,彼此相关的。而且这些与你的芯片的电气特性、PCB上的传输线以及厚度等是密切相关的。用仿真工具可以很容易看到过孔对信号的影响。如果你要计算的话,工作量是非常大的。

八、1、您不建议在走线密集的信号层大面积敷铜的主要考虑是什么?

2、如果我要对一些高频信号(比如时钟信号)用敷铜接地来与其他信号隔离,是否就在其走线周围局部敷铜接地更好?

1 已经是走线密集了,还怎么大面积敷铜?

2 如果你要对一些高频信号进行隔离,在这些信号的两边走地线就可以了,也不用敷铜。敷铜会占用较大的布线空间,而且效果未必好。

九、关于传输线的阻抗匹配我始终有些问题,比如一个USB的D+和D-信号(现在给他们端接的电阻都为22欧姆)

1、这个22欧姆的匹配电阻是怎么计算得出的?

2、如果我将这两个电阻去掉会对信号有什么影响?而如果我将其阻值改为50欧姆又会出现什么情况?

3、源端和负载端的阻抗是怎么计算的?怎么用他们来确定要用来匹配的电阻的值?

1 我对USB没有仔细的研究,你说的端接是指源端端接?不过我想这个22欧姆的电阻主要是根据PCB上的走线以及USB芯片的电气特性得出的。

2 你说的端接是指源端端接的话,并且22欧姆是良好匹配,你去掉这个电阻会看到信号会有过冲。换成50欧姆,信号沿将变的很缓,影响USB的性能。

3 源端和负载端的阻抗是芯片的特征,一般根据IBIS模型可以得出其相应的特征。一般来说要求源端阻抗、传输线阻抗以及负载端的阻抗一致,如果不一致的话,就需要进行匹配,匹配电阻的值,就是根据这几个阻抗的差别来确定的。

十、我还是不太明白,难道SOCKET370的引脚定义可以自己定义使用吗,INTEL应该有完全的定义方式吧?哪里有SOCKET370的用户手册?

再问一个问题:数字地(电源)和模拟地(电源)有甚摸具体意义上的区别,它们两个如何相互连通和使用。

你可以到intel的网站上去查找一下,你也可用google到internet 上去查找有关socket370的资料。

关于数字地和模拟地主要是因为它们回流的路径不一样以及为了避免相互之间的干扰,需要对它们进行分开布局布线,最后通过一点将它们连接起来。

十一、我现在有一个实例问题如下: 一个数码相机用CCD的模拟电源输入端AVDD1--AVDD5,这些pin脚都应该给3.3V的输入;现在是这么连接的,从AVDD1到AVDD5分别串接一个0欧姆电阻,然后才联接到A3_3V;所有的去藕电容都是连接到A3_3V这一端,而不是直接连到AVDD1到AVDD5的pin脚上,中间被0欧姆电阻隔开了;

1、我现在不明白为什么要串接0欧姆电阻,这样的意图是什么?如果是这样的话,去耦电容将离CCD的AVDD1--AVDD5这些管脚较远;这对信号质量的影响是否较大?

2、把0欧姆电阻去掉,将AVDD和A3_3V直接相连,这样是否更好?

是0欧姆电阻还是用的磁珠? 如果是磁珠的话,那是为了防止两边的噪声互相干扰。如果是0欧姆电阻的话,我也不清楚,估计只有设计人员才知道了。

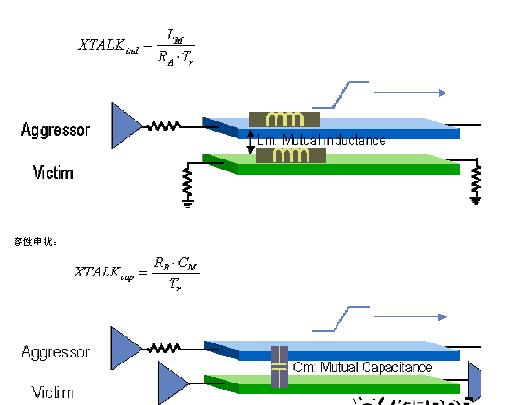

十二、请教专家,什么叫做容性串扰和感性串扰?分别产生的原理以及对信号产生的影响如何?我们在设计高速PCB时又怎样来减小这些串扰?应该注意那些问题?

简单地讲,由于导体之间的互容参数而引入的串扰为容性串扰而由导体之间的互感分量而引入

的串扰称为感性串扰。其计算公式如下:

感性串扰:

容性串扰:

为了减少串扰可以采取很多措施,如拉大线间距,加匹配电阻,采用差分技术等等。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)