引言

多节点系统,在目前的很多电子系统应用场合都可以看到。这种多节点系统由于具有结构可扩展性、功能配置的灵活性以及便于查找故障节点等良好的可维护性得到了越来越广泛的应用。通常,多节点系统各个节点的主要硬件构成有很大的相似性。特别是近年来, FPGA这个强大的平台让多节点系统各个节点的硬件构成拥有了更广泛的通用性。尤其是随着IP核技术的推广,再加上一些功能强大的CPU核的出现,如 Xilinx公司提供的PicoBlaze和MicroBlaze等,使得目前的许多系统的主要功能都可以由大容量的FPGA实现,而无需再使用比较昂贵的高性能微处理器。

对于节点系统,这将大大降低系统成本。对于由大容量FPGA构成的多节点系统,系统的升级是一个费时费力的工作。此时,FPGA的远程升级能力就显得尤为重要。对于包含arm、DSP、PowerPC等高性能嵌入式微处理器的多节点系统,使用这些嵌入式微处理器,采用SELECTMAP对FPGA进行加载并实现远程升级,无需增加过多的外部器件,是非常经济和高效的。但对于核心器件就是大容量FPGA的系统,如果由FPGA本身来接收升级数据并写入存储配置数据的非易失性存储器,一旦升级失败,将无法再次升级,从而限制了它在许多需要高可靠性要求或者维护人员不便于到达的场合的应用;而如果单纯为了实现系统的远程升级而加入价格昂贵的嵌入式微处理器,又会较大地增加系统成本和复杂性。针对这种情况,笔者设计了利用ATmega64单片机和RS485总线,加上接入以太网的主控计算机构成的远程升级系统,解决了上述问题。

1 系统设计

1.1 系统结构设计

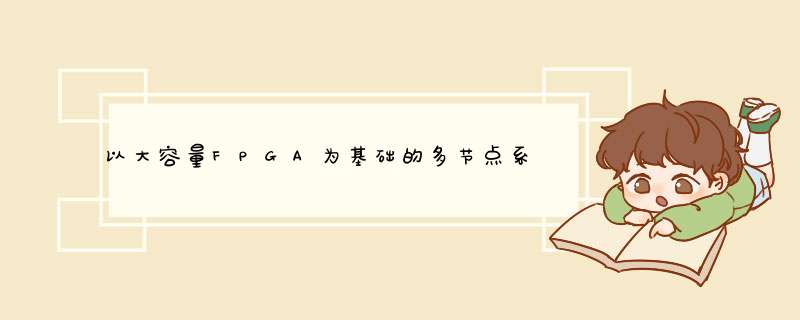

远程升级系统主要由一台接入以太网的主控计算机、半双工RS485总线以及各个子节点构成,组成结构如图1所示。主控计算机通过以太网从外部获取整个系统各个节点的升级数据,然后通过RS485总线向各个子节点发送其对应的升级数据,完成多节点系统的升级。RS485总线采用一主多从的半双工方式,主控计算机为总线的主控制器,只能由它向各个节点发起通信连接,其余子节点只能响应主控计算机的控制命令。

图1 多节点大容量FPGA系统远程升级系统结构框图

1.2 节点升级原理

各个节点通过RS485总线与主控计算机相连,在无升级数据时,总线可以用来传输主控计算机对各个节点的查询和控制命令。主控计算机与各个节点的通信协议可以采用具有查询控制帧、应答帧和数据帧3种帧类型的协议。只有主控计算机可以发送查询控制帧,查询或设定各个节点的远程升级状态或工况信息。子节点接收主控计算机的命令和数据,发送应答帧,并完成自身的升级。

2 子节点的硬件设计

2.1 子节点硬件结构框图

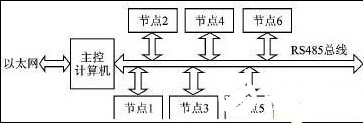

如图2所示,以一个由Xilinx公司的XC3S4000大容量FPGA构成的系统为例,远程升级系统子节点的硬件电路主要包括: ATmega64单片机,用于存储大容量FPGA配置数据的Flash,以及接入RS485总线的半双工总线收发器。ATmega64单片机用于实现对大容量FPGA XC3S4000的加载,以及从RS485总线接收FPGA的升级数据并写入拥有2 MB存储空间的Flash存储器SST36VF1601C中。RS485TTL电平变换电路采用RS485收发器SP485R。

图2 子节点硬件结构框图

2.2 子节点硬件设计说明

在子节点的硬件设计中,ATmega64单片机是实现整个升级功能的关键。ATmega64是基于增强的AVR RISC结构的低功耗8位CMOS微控制器。由于其先进的指令集以及单时钟周期指令执行时间,ATmega64 的数据吞吐率高达1 MIPS/MHz,从而可以缓解系统在功耗和处理速度之间的矛盾。AVR内核具有丰富的指令集和32个通用工作寄存器,并且所有的寄存器都直接与算术逻辑单元(ALU)相连接,使得1条指令可以在1个时钟周期内同时访问2个独立的寄存器。这种结构大大提高了代码效率,并且具有比普通的CISC微控制器最高至10倍的数据吞吐率。ATmega64有如下特点:

① 64 KB的系统内可编程Flash(具有同时读写的能力,即RWW),2 KB的EEPROM,4 KB的SRAM,32个通用工作寄存器;

③ 实时计数器(RTC);

④ 4个具有比较模式与PWM的灵活的定时器/计数器(T/C),具有片内振荡器的可编程看门狗定时器;

⑤ 2个USART,面向字节的双线串行接口(TWI),1个SPI 串行端口;

⑥ 8路10 位具有可选差分输入级可编程增益的ADC;

⑦ 与IEEE 1149.1 标准兼容的,可用于访问片上调试系统及编程的JTAG接口。

ATmega64是以Atmel 高密度非易失性存储器技术生产的。片内ISP Flash 允许程序存储器通过ISP 串行接口(或者通用编程器)进行编程,也可以通过运行于AVR内核之中的引导程序进行编程。通过将8位RISC CPU与系统内可编程的Flash集成在一个芯片内,ATmega64 成为一个功能强大的单片机,为许多嵌入式控制应用提供了灵活而低成本的解决方案。

利用ATmega64单片机实现对大容量FPGA的远程升级,涉及的主要技术问题有三点:一是如何将ATmega64单片机接入RS485总线;二是在接收到升级数据后和加载FPGA时,如何利用ATmega64单片机对大容量的Flash存储器进行读写 *** 作;三是ATmega64单片机实现 FPGA的SELECTMAP加载。

2.2.1 RS485接口电路设计

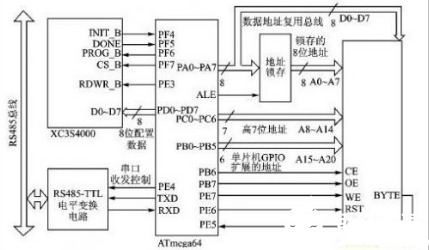

如表1所列, RS485总线标准具有控制方便、价格低廉以及高噪声抑制、相对高的传输速率、传输距离远和宽共模范围等优点。在过去的20年时间里,建议性标准RS485作为一种多点差分数据传输的电气规范,被应用在许多不同的领域作为数据传输链路。

表1 TIA/EIA485串行通信标准的性能

子节点的ATmega64单片机通过Sipex公司设计生产的高性能RS485收发器接入RS485总线。

SP485R是一款与流行的标准RS485芯片完全兼容,而且包含更高的ESD保护和高接收器输入阻抗等性能的RS485收发器。接收器输入高阻抗可以使400个收发器接到同一条传输线上,又不会引起RS485驱动器信号的衰减。该收发器的特点如下:

① 允许超过400个收发器接到同一条传输线上;

② 接收器输入高阻抗(标准值RIN=150 kΩ);

③ 半双工配置与工业标准引脚一致;

④ 共模输入电压范围为-7~+12 V;

⑤ 低功耗(250 mW);

⑥ 独立驱动器和接收器使能引脚。

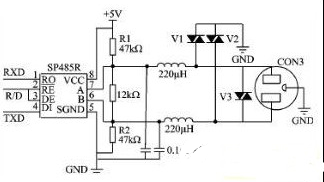

其典型应用电路如图3所示。

图3 利用SP485R构成的半双工RS485电路

ATmega64单片机的标准串行口通过RXD直接连接SP485R芯片的RO引脚,通过TXD直接连接SP485R芯片的DI引脚。由单片机输出的R/D信号直接控制SP485R芯片的发送器/接收器使能:R/D信号为1,SP485R芯片的发送器有效,接收器禁止,此时单片机可以向 RS485总线发送数据字节;R/D信号为0,SP485R芯片的发送器禁止,接收器有效,单片机可以接收来自RS485总线的数据字节。上拉电阻R1、下拉电阻R2用于保证未连接总线时的SP485R芯片处于空闲状态,以提高每个RS485节点的工作可靠性。6.8 V的TVS管V1、V2、V3用来保护RS485总线,避免RS485总线受外界干扰时产生的高压损坏RS485收发器。

2.2.2 ATmega64存储空间的扩展

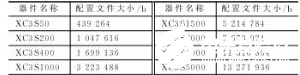

ATmega64的寻址空间为64 KB,利用ATmega64自身的寻址系统,只能访问0x0000~0xFFFF的地址空间。显然,这对于存储和加载大容量FPGA的配置数据是远远不够的。以Xilinx公司的Spartan3系列FPGA为例,其配置数据所需的存储空间如表2所列。

表2 Spartan3系列FPGA配置文件大小

以XC3S4000型FPGA为例,它的配置文件所需的存储空间约为1.35 MB,已远远超出了ATmega64单片机的寻址空间。因此,为了能够利用ATmega64单片机来实现对FPGA配置数据的读写,必须对其寻址空间进行扩展。扩展的硬件连接框图如图2中的单片机与Flash的连接部分所示。

本设计中是使用通用I/O来扩展ATmega64单片机的寻址空间的。ATmega64单片机的总寻址空间为64 KB,但片内4 KB的SRAM及各种寄存器占用了前面的部分寻址空间,故其片外存储器寻址空间是0x1100~0xFFFF。因此将Flash的低15位地址直接接到 ATmega64单片机的低15位地址总线上,其余6位高位地址用单片机的通用I/O进行选择。寻址时单片机的专用地址口只输出 0x8000~0xFFFF的地址数据,与通用I/O输出的地址组合后给出Flash的读写地址。

通过以上对ATmega64单片机寻址空间的扩展方法,可以实现ATmega64单片机对合适的Flash存储器的寻址 *** 作,从而解决了大容量FPGA配置数据的存储和读取问题。

2.2.3 用ATmega64实现FPGA的SELECTMAP加载

Xilinx公司的Spartan3系列FPGA加载方式分为5种: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照FPGA是否控制加载过程,加载方式可分为Master方式和Slave方式;按照加载数据时的数据位宽,可分为Serial方式和 Parallel方式。用于加载的引脚主要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP和JTAG接口(TDI、 TMS、TCK、TDO)。加载过程大体分为3个步骤:配置的建立、配置数据的加载和加载完成。

SELECTMAP即Slave Parallel方式,是由外部控制器控制FPGA的加载过程,并以8位数据的形式向FPGA写入加载数据的加载方法。图2中FPGA与ATmega64 的连接部分为ATmega64单片机采用SELECTMAP方式对FPGA进行加载的硬件连接框图,具体实现过程如下:

ATmega64通过将FPGA的PROG_B、CS_B和RDWR_B引脚置低来开启加载过程,FPGA在PROG_B置低后开始清除内部配置RAM,并将INIT_B脚置低。PROG_B重新置1后,在INIT_B由低变高的上升沿,FPGA采样M[0~2]引脚获取配置方式信息。 ATmega64监视FPGA的INIT_B脚,当INIT_B脚由低变高时,说明FPGA已经完成了内部配置RAM的清除工作,并准备好接收配置数据。在ATmega64给出的CCLK配置时钟的上升沿,配置数据D[0~7]写入配置RAM。当FPGA接收完所有的配置数据后,DONE引脚被FPGA置为高电平。ATmega64可以通过监视DONE引脚来判断FPGA是否加载完成。对于Spartan3系列的FPGA,如果配置FPGA的CCLK的频率高于50 MHz,则外部控制器还需要监视FPGA的BUSY引脚。当BUSY脚为高时,说明FPGA还未完成上一个配置数据的处理,此时外部控制器需要继续保持上一个配置数据在D[0~7]引脚,直至BUSY引脚回到低电平。对于本设计的应用,ATmega64给出的配置时钟频率远低于50 MHz,不必考虑BUSY引脚的控制作用。

3 软件设计

3.1 主控计算机的软件设计

主控制计算机的软件运行状态应该分为两种:一是平时的查询控制状态,用来查询和控制系统中各个节点的工作状态;二是系统的升级状态,用来执行对各个子节点的升级控制。如图4所示,这两种状态是可以相互转换的。

图4 主控计算机主要状态

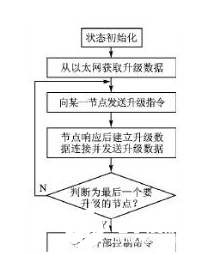

软件的查询控制状态,是由系统所要实现的主要功能决定的,不属于本文所讨论的范畴。在系统的升级状态,主控计算机先要通过以太网获得系统各个节点的远程升级数据,待全部升级数据接收完成后,向系统的一个节点发送升级指令。节点响应并建立起通信连接后,将该节点的升级数据全部发送到该节点。接下来,主控计算机判断上一个节点是否为最后一个需要升级的节点,如果不是,则继续进行下一个节点升级数据的传输。系统所有的节点升级完成后,等待外部输入的控制命令。例如,让整个系统重新启动,加载新的数据;或暂时不重新启动而返回查询控制状态。软件流程如图5所示。

图5 系统升级状态流程

3.2 子节点的软件设计

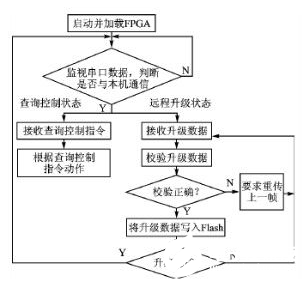

对于子节点的软件设计,与主控计算机一样,也分为平时的查询控制状态和系统升级状态,并且它们之间也能够与主控计算机一起相互转换;但 ATmega64单片机还要承担对FPGA的加载任务。开机运行后,ATmega64单片机先加载子节点FPGA,使子节点能够正常工作。子节点正常工作后,监视RS485总线并判断有无对本节点的通信。当主控计算机要求与本节点建立通信连接时,发送反馈信息,与其建立通信连接。子节点根据主控计算机发送的命令,进入查询控制模式或者远程升级模式。进入远程升级模式后,子节点接收主控计算机发来的远程升级数据,升级数据经过校验后写入Flash。升级完成后继续等待主控计算机的命令,重新启动或继续运行。其具体的软件设计流程如图6所示。

图6 子节点软件流程

结语

FPGA既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC周期长、投资大、灵活性差的缺点,逐步成为许多系统实现的理想选择。特别是随着FPGA容量和性能的提升,加上其独特的硬件升级能力,其应用范围越来越广。本文所提出的对大容量FPGA构成的多节点系统的远程升级方法,系统构成简单、技术成熟,而且具有明显的成本优势。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)