0 引言

近些年来,由于其灵活可配置性及成本的降低,现场可编程门阵列(Field Programmable Gate Array,FPGA)在嵌入式系统中应用越来越广泛,不论产品的初期研发或是后期维护都不可避免地需要频繁更新FPGA程序。传统的JTAG方式更新FPGA程序的方式是通过开发软件将需固化的文件写入Nor Flash器件。当系统很复杂且需要更新的FPGA数量较多时,JTAG方式更新FPGA程序则费时费力且还需拆结构。若在FPGA内部通过逻辑代码搭建一Flash控制器实现对Flash器件的读写 *** 作,即可并行实现系统内每片FPGA对配置文件的在线更新,大大缩短程序固化时间。本文依托于Xilinx公司的FPGA和Spasion公司的Nor Flash,详细介绍了Flash控制器设计和在线加载功能的实现方法。

1 FPGA配置方式

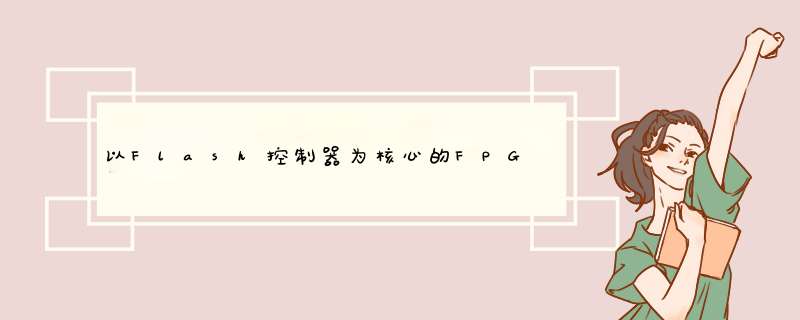

以Xilinx Virtex6 系列FPGA为例,对配置文件的加载方式有串行Flash、并行Flash、JTAG方式等,其中最常用的是并行Flash方式(Byte Peripheral Interface Parallel Flash Mode,BPI),其配置模式如图1所示。

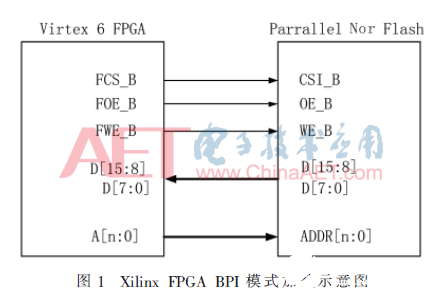

一种实际的FPGA与Nor Flash硬线连接方式如图2所示。

无论是通过JTAG方式还是通过软件 *** 作实现程序更新,都是通过控制这些读写使能信号及地址线实现配置文件的写入,FPGA掉电重启之后再从Flash取出配置数据从而实现加载。本文提出的FPGA在线更新程序的方式则是通过FPGA控制逻辑驱动Flash的数据和地址,从而为多块FPGA并行更新程序的实现提供了前提。

2 Flash控制器设计

Flash器件的基本 *** 作包括读、写、擦除等,这些 *** 作都是通过向相应的命令寄存器写入特定的指令来实现的,这些指令的写入通过 *** 作与FPGA相连的片选信号(ce_n)、写使能信号(we_n)、读使能信号(oe_n)、地址总线(addr[23:0])和数据总线(dq[15:0])实现。

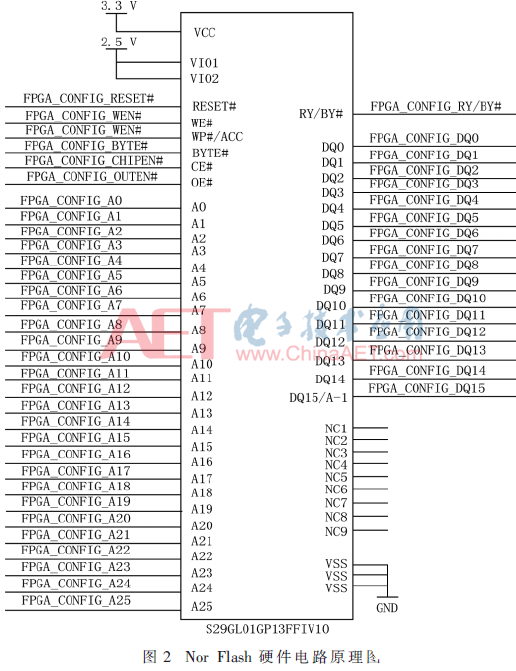

以目前市场上常用的Spasion公司的S29GL-P系列Nor Flash为例,通过FPGA实现的控制器外部接口如图3所示。

其中,start信号用于启动控制器模块对Flash器件实现读写 *** 作,在启动之前,须先告知Flash配置文件大小和配置文件在Flash存储空间的首地址;data_req、data_in和rd_data_count信号用于与一前端FIFO实现数据交互,配置文件先缓存到FIFO中,然后由控制器负责取出并写入Flash器件;config_status信号用于指示程序更新是否完成。

该Flash控制器按时间上的先后顺序分别实现了对Flash器件的读ID、擦除和写缓冲 *** 作,下面将分别进行简要叙述。

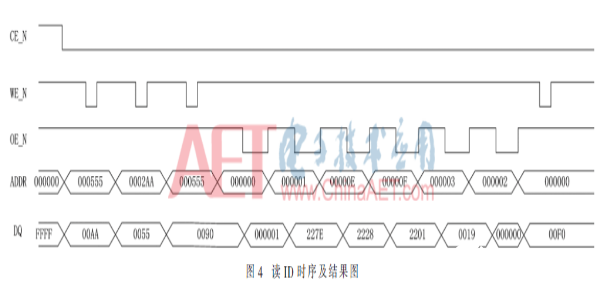

每次对Flash进行基本的读写 *** 作之前,会对Flash芯片进行读ID *** 作以检验器件的好坏,读ID涉及的主要 *** 作为向特定寄存器写入相应的解锁指令,然后再进行多 *** 作读出相应的寄存器值,其时序图及读结果如图4所示。

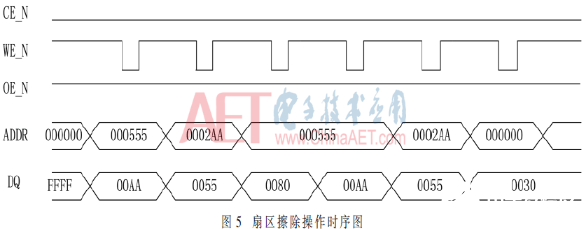

确认了芯片ID无误,即可进行正确访问,首先对Flash芯片进行擦除 *** 作。Flash芯片擦除可分为两种:整片擦除和扇区擦除。由于实际使用时并未用到整块Flash存储空间,而是根据配置文件的大小选择合适的扇区大小存储配置文件,所以设计中采用的是扇区擦除方式,时序如图5所示。

当成功写入擦除 *** 作指令之后,芯片会进入一个较长的周期等待擦除 *** 作的完成,该期间无法对芯片进行复位之外的其他 *** 作。

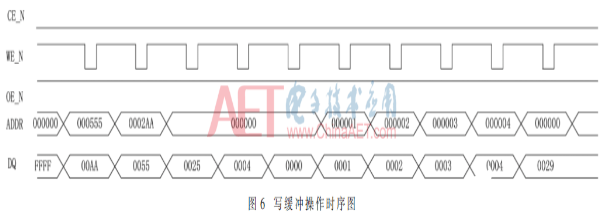

完成了擦除 *** 作之后,即可向Flash写入配置数据,其对应的写缓冲时序如图6所示。

擦除和读写的过程中,地址将进行自动累加且起始地址可变。Flash的写 *** 作可为单字写和缓冲写两种,由于缓冲写最大一次可向Flash写入32个字,为了最大化写入速度,选择缓冲写方式;Flash的读 *** 作分为单字读和按页读两种,由于Flash读数据速率较高且系统对读速率没有太高要求,本文选择单字读方式。

3 工程应用及性能测试

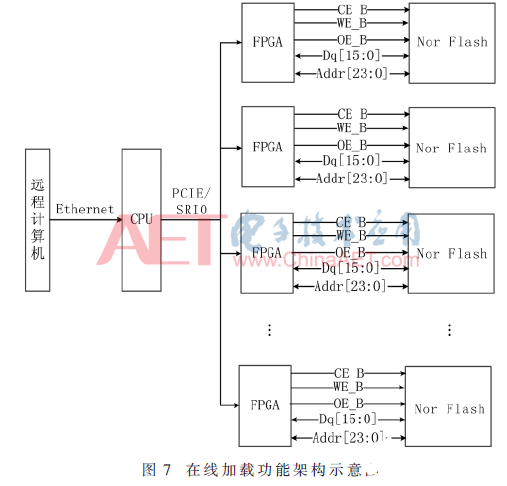

以一实际项目工程为例,系统中具有10块FPGA进行程序更新,其在线加载功能系统架构如图7所示。

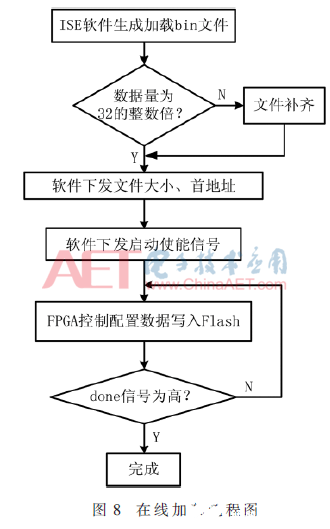

系统主控CPU运行在Linux系统下,CPU通过以太网与远程计算机进行通信调试,同时通过PCIE或SRIO高速总线向每块FPGA下发配置数据,最后再由Flash控制器完成数据的写入。如前文所述,一次写缓冲 *** 作的数据量为32个字,而配置文件的大小有可能不是32个字的整数倍,所以还需要应用软件对配置文件进行补齐 *** 作。单个FPGA在线加载流程简要叙述如图8所示。

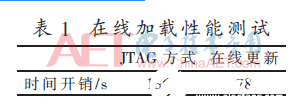

更新单块FPGA程序时,以一实际测试的3.47 MB大小的配置文件为例,经FPGA在线更新程序固化的时间和使用ISE14.7软件JTAG方式固化的时间如表1所示。

Flash芯片手册中给出的典型擦除和写缓冲时间分别0.5 s和480 μs,则可计算出理论上3.47 MB大小的文件固化所需的典型时间约为41 s。由于器件等因素影响,实测时用时往往大于该时间,但总体来说,使用在线更新方式的耗时要比用JTAG方式耗时更少。

而当更新系统中的10块FPGA时,由于每块FPGA均可同时进行在线更新 *** 作,程序固化所消耗的时间与单块FPGA程序更新时间开销大致相当,可见并行在线更新方式相较于传统JTAG方式无疑可以大大缩短时间。

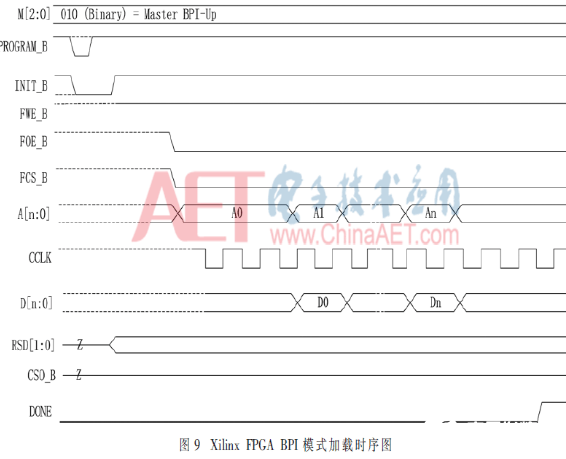

4 配置文件不断电加载和备份方法

每次更新完配置之后,通常做法是对FPGA进行断电重启实现重新加载,但工程应用时断电可能会影响系统其他模块的正常工作。为使FPGA在不断电的情况下自动加载更新完的配置程序,可通过配置FPGA芯片的PROGRAM_B信号来实现,BPI模式下的时序如图9所示。

考虑到若在配置过程中FPGA发生断电等异常,则Flash中的配置文件损坏,FPGA将无法实现加载,需要重新使用JTAG方式烧写配置文件。为防止该种情况发生,可分配Flash的一块区域用于备份配置文件,发生FPGA无法正常加载的异常时,可读取该备份配置文件实现FPGA再次正常加载,但前提是该部分Flash存储空间预先固化了带有FPGA在线更新功能的程序。

5 结论

本文利用FPGA逻辑设计了一款Flash控制器,实现了FPGA在线更新功能,由于FPGA直接 *** 作Flash,因此相比传统FPGA程序更新方法具有更新速度快、硬件电路精简、易于系统集成等优点,同时能够实现复杂系统多块FPGA并行更新程序,大大节省了程序固化时间,便于项目前期开发及后期排故调试。

参考文献

[1] Xilinx UG360,Virtex-6 FPGA configuraTIon user guide[EB/OL]。[2015-11-18].http://www.xilinx.com.

[2] Spansion.S29GL-P MirrorBit Flash family datasheet[EB/OL]。[2009-11-20].http://www.spansion.com.

[3] 于乐,王嘉良。易于移植的FPGA在线更新控制器设计[J]。航空电子技术,2015(4):47-50.

[4] 杨鹏。基于Linux系统的FPGA芯片在线加载的设计和实现[J]。电子设计工程,2015(6):161-164.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)