由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

1》AXI_LITE协议:

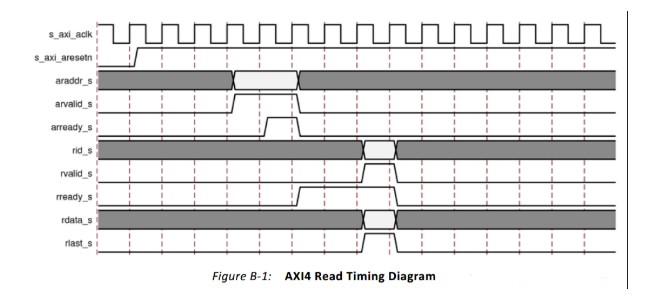

( 1) 读地址通道, 包含ARVALID, ARADDR, ARREADY信号;

( 2) 读数据通道, 包含RVALID, RDATA, RREADY, RRESP信号;

( 3) 写地址通道, 包含AWVALID, AWADDR, AWREADY信号;

( 4) 写数据通道, 包含WVALID, WDATA, WSTRB, WREADY信号;

( 5) 写应答通道, 包含BVALID, BRESP, BREADY信号;( 6) 系统通道, 包含: ACLK, ARESETN信号。

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A: address; R: read)写地址信号都是以AW开头( A: address; W: write)读数据信号都是以R开头( R: read)写数据信号都是以W开头( W: write)

XI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A: address; R: read)写地址信号都是以AW开头( A: address; W: write)读数据信号都是以R开头( R: read)写数据信号都是以W开头( W: write)

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A: address; R: read)写地址信号都是以AW开头( A: address; W: write)读数据信号都是以R开头( R: read)写数据信号都是以W开头( W: write)

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A: address; R: read)写地址信号都是以AW开头( A: address; W: write)读数据信号都是以R开头( R: read)写数据信号都是以W开头( W: write)

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A: address; R: read)写地址信号都是以AW开头( A: address; W: write)读数据信号都是以R开头( R: read)写数据信号都是以W开头( W: write)

AXI_LITE读时序:

AXI_LITE:写时序

2》AXI_STREAM:

AXI4-Stream总线的组成有:

( 1) ACLK信号: 总线时钟, 上升沿有效;

( 2) ARESETN信号: 总线复位, 低电平有效

( 3) TREADY信号: 从机告诉主机做好传输准备;

( 4) TDATA信号: 数据, 可选宽度32,64,128,256bit

( 5) TSTRB信号: 每一bit对应TDATA的一个有效字节, 宽度为TDATA/8

( 6) TLAST信号: 主机告诉从机该次传输为突发传输的结尾;

( 7) TVALID信号: 主机告诉从机数据本次传输有效;

( 8) TUSER信号 : 用户定义信号, 宽度为128bit。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)