2013年12月10日,赛灵思全球高级副总裁汤立人先生专程到中国北京和深圳等地与各地媒体沟通, 隆重宣布赛灵思一个崭新的产品系列 ——All Programmable UltraScale的正式面世。其中包括两项重要内容:

1. 发布完整的20nm All Programmable UltraScale产品系列阵容,而且已经开始发货其中一款器件, 并拥有相关文档、选型表以及行业唯一SoC增强型设计套件Vivado的支持。

2. 宣布了一个新的创纪录的突破性器件——拥有440万逻辑单元的器件,其容量相比之前发布的全球最大容量器件Virtex-7 2000T翻了一番。

这两项新的发布有何意义, 赛灵思人为何如此激动万分地、骄傲无比地进行如此大张旗鼓的全球发布呢?我们又该如何理解此次发布呢? 让我们试着解读一下:

解读一: 新的UlstraScale产品阵容的发布,再次强化了其从28nm就开始的领先一代领导者地位

在28nm工艺节点,从2011年3月赛灵思发货全球首个 28nm 器件 — Xilinx Kintex-7® 325T FPGA开始, Xilinx 是一路领先,用一个个行业第一的发布把竞争对手远远地抛在了身后,包括行业第一个HPL 工艺, 包括行业第一个双ARM A9核 All Programmable So C, 包括行业第一3DIC, 行业第一个面向未来十年的All Programmable设计工具等。从40nm短暂的阴霾中胜利突围,打破了竞争对手当时“后来居上”的美梦。28nm的收入也持续攀升, 在最近的两个季度已经拥有70%以上的市场份额。无论从工艺还是收入各个方面,赛灵思在28nm领域已经实现了领先一代的优势。

而在20nm工艺节点, 从7月的行业首个投片,11月的首个发货,赛灵思走上了继续领先一代的道路。

解读二:新的产品阵容,加速了赛灵思也是FPGA取代ASIC/ASSP的步伐

赛灵思此次发布的大背景,建立在其从28nm就已经开始的从“可编程逻辑设计公司”到‘ALL PROGRAMMABLE” 公司的转型战略之下。 赛灵思的产品从单纯的FPGA发展到了FPGA, 3D SoC, 超越了数字到模拟,超越了可编程硬件到软件,超越了单芯片到3DIC。所有赛灵思芯片产品(如All Programmable FPGA、3D IC和SoC)的基础构建模块在28nm工艺节点已达到一个临界阈值。这个阈值标志着FPGA无论从规模还是速度方面均已经发展到了足以实现整个系统的水平。在28nm工艺节点上,赛灵思的解决方案能够取代整个ASSP和ASIC,这就是说赛灵思All Programmable器件配备合适的IP和软件,能够成为实现众多最终产品所需的唯一重要集成电路器件。

然而28nm只是开始,取代ASIC/ASSP还需要更多突破, 其中最大的就是互联问题, 而UlstraScale消除了互联这一首要的瓶颈。 7月,当宣布行业首款20nm 器件投片的同时, 也宣布 20nm 将采用的全新架构——行业首个ASIC级架构UlstraScale。

作为FPGA的发明者, FPGA这个崭新领域的开拓者, 赛灵思不仅引领着FPGA技术的发展, 也引领者应用拓展。它的战略眼光早已超越了几十个亿的PLD市场和这个领域的竞争者,投向上百亿美元的ASIC/ASSP 和嵌入式市场领域。由此可见,此次拥有ASIC级架构、ASIC级设计方案的All Programmable UltraScale 产品阵容的发布,是其战略性加速进军ASIC/ASSP市场的一个里程碑式成就。ASIC 级架构的器件,全新打造的All Programmable Vivado 设计套件,加上加速上市和提升了结果质量的一套UlstraScale 设计方法, 提供了媲美ASIC的优势。 赛灵思怎能不骄傲和自豪呢?

解读三:当我们看赛灵思的发布的时候, 大家很自然地会和其最近的竞争对手相比。但是,在比较的时候,请大家不仅仅只是比工艺。

今天的发布, 是一个加速取代ASIC/ASSP 的全新产品系列, 20nm工艺之外, 重点是ASIC级的优势。 这个优势是如何实现的呢?看下图, UlstraScale ASIC级的架构, Vivado设计工具, 再加上UlstraFast设计方法, 三者的统一才实现了ASIC级的优势。 而这三者的结合, 实际上也体现了赛灵思致力于支持更多工程师加速上市和实现差异化的方法和思路。

——ASIC级的架构是根本, 提供了ASIC级的性能, 支持海量的数据流, 同时消除了最大的互联瓶颈。

——行业首个ASIC++增强型工具套件Vivado,加速了集成和实现。 尤其是Vivado独特的HLS (高层次综合) 和IPI ( IP 集成器), 通过C++语言自动转化为RTL 和固化的IP让之前只有硬件工程师的FPGA世界,为庞大的软件工程师和系统工程师群体打开了大门。

——产品上市时间和成本很大程度上取决于开发人员如何运用工具解决新一代复杂性问题,因此赛灵思定义了一套All Programmable设计方法 —UlstraScale 设计方法。该方法涵盖最佳实践以及一系列项目规划、开发板布局和器件规划的项目表,同时能应对设计创建、实现和配置调试等诸多挑战,从而帮助工程师提高了设计生产力与效率,加速了产品上市进程,并提升了结果质量(QoR)。

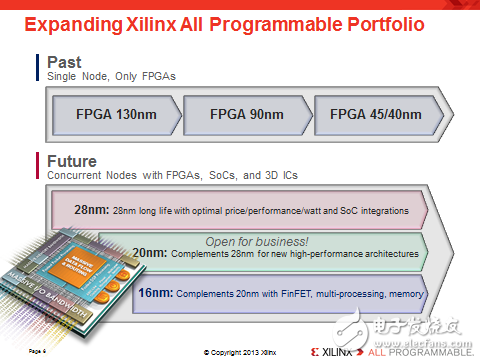

解读四:新的产品系列的发布主要针对的是打造高性能的Smarter System。 28nm并不会因为这个发布而成为过去。实际上, 28nm真正上量是在2014年, 赛灵思融FPGA,SoC, 3DIC 为一体的28nm产品系列具有很长的生命周期, 至少15年都会长期存在。

解读五:了解赛灵思产品战略上的一个转变, 从FPGA 到All Programmalbe 。从以前的单工艺节点只有FPGA, 发展到多种工艺共存, 三大产品系列(FPGA,SoC, 3DIC)共同发展。

Virtex UltraScale VU440为新一代生产和原型设计应用提供了5000万个ASIC等效门,树立了全新的行业标杆。20nm Virtex UltraScale器件还为400G MuxSAR、400G转发器和400G MAC-to Interlaken 桥接器应用的单芯片实现方案提供了最高系统性能和带宽。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)