过去,我们在讨论音频话题时,偶尔会提及 I2S。我在以前的一些文章中提到过 I2S,其他人在做音频研究时也都会提到它。简而言之,它是一种将立体声数据从一端传输至另一端的同步方法。

大多数人认为 I2S 有三种信号:

1.数据:输入或者输出数据

2.位时钟 (Bitclock,BCK):确立数据流中两个相邻位之间边界的信号

3.左/右时钟 (LRCK)/字时钟 (Wordclock):一个在采样速率下运行、占空比为 50% 的慢时钟,它确立数据流中两条相邻通道(左和右)之间的边界。

I2S的幕后英雄是主时钟 (MCK),也称作系统时钟 (SCK),它常常被数字信号处理器 (DSP) 程序员和其他处理器爱好者们忽略。主时钟 (MCK/SCK),通常为一个64、128、256和512倍采样速率 (FS) 的时钟。它可以由一个输入引脚直接提供,也可以通过一个锁相环路 (PLL) 在某些器件内部产生。

一般而言,DSP不需要音频主时钟,因为它们能够以一种完全不同的速率对数据进行处理,然后在BCK和LRCK的驱动下,让数据以某种速率进入输出缓冲器(或者通过输入缓冲器接收数据)。

如果您能暂时将注意力从您的处理器上移开,您会发现音频主时钟重要得多。大多数MCK/SCK输入的音频转换器,都要求时钟同步,而有一些则允许异相位。这就意味着,它们需要由相同的高速时钟来提供,然后被除小。我接触过的一些客户会突发灵感地告诉我:“我的ADC需要一个MCK,但它离我的DAC太远。因此,我要在每个转换器旁边放置一个晶体……”有这种想法可以理解,但请您“千万别这么做!”

您在购买晶体时,无法保证它刚好为48.000 kHz。您的模数转换器 (ADC) 晶体的运行精确度可能会为+5%,而数模转换器 (DAC) 的运行精确度可能为–5%。这样的精确度,会给您的设计带来灾难性的后果!这是为什么呢,下面将为您娓娓道来。

用于 I2S

用于音频ADC的主时钟

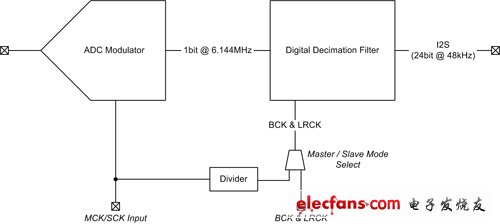

如图1所示,高速主时钟(例如:24.576 MHz时钟)用于驱动ADC的过采样调制器。之后,来自过采样调制器的数据被消减分解成LRCK给定的采样速率。

当ADC运行在主模式(生成BCK和LRCK,作为输出)下时,ADC只是对MCK/SCK进行划分,产生LRCK和 CK信号。这就对啦!LRCK/BCK和主时钟被同步—相位也可能同步(除非它是一个特殊分割器)。

图1 通用ADC结构图

如果作为一个从器件,并且主时钟不同步,则它产生的数据会过多或者过少,以至于数字抽取器无法刚好适合于输出字。在这种条件下,许多ADC会拒绝流传输数据。

DAC也是如此。图2显示了一个高级DAC结构图。此处,需要通过MCK/SCK运行内插器,而MCK/SCK同时还驱动△∑调制器。如果MCK/SCK不是采样速率的整倍数 (64/128/256/512),则在△∑调制器输出端可能会出现错误数据。

图2 通用DAC结构图

我在哪里/如何生成MCK/SCK呢?

在当今的工业应用中,CMOS振荡器由许多晶体振荡器支持,并紧靠这些晶体振荡器。它们都拥有非常好的精确度和较低的抖动。偶尔会用到压控振荡器 (VCO),但它们会受到其输出抖动的困扰。

许多现代的音频转换器现在都集成了一个PLL,以通过慢BCK产生MCK。这样做很有效。但是,您应该注意,使用PLL时始终都会有产生抖动的可能,从而降低了音频性能。

另外,我建议,如果在晶体源驱动ADC或是DAC两者之间选择,请您选择通过一个晶体产生源来运行ADC。如果输入很糟糕,那么您做什么都于事无补!(就像您不可能把烂泥打磨光亮!)

因此,我的建议遵循的原则是:

1、如果转换器为一个I2S从器件,则您必须通过相同源(如果转换器带有,则可以依靠内部 PLL),提供所有三个I2S时钟(MCK、BCK和LRCK)。

2、如果转换器为一个I2S主器件,则请确定能够提供一个可靠的无抖动MCK源。然后,让转换器自己分配。在可能的情况下,让ADC通过一个可靠的低抖动MCK源在主模式下运行。这样做可以确保最低抖动和最小高频失真。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)