简 述

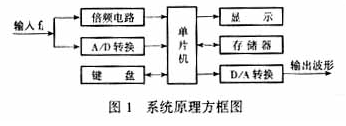

移相电路常用于同步检测器的数据处理中。目前资料上有很多移相电路,其实现方法多种多样,大致可分为模拟式和数字式移相器两类。模拟式移相器的电路较为复杂、线性差、测试精度低;数字式移相器大多以标准逻辑器件按传统数字系统设计方法设计而成,其缺点为功耗大、可靠性低。本文介绍的基于单片机控制的数字移相器,采用环形队列实现信号波形的任意相位移相,并且保持波形的幅度、频率不变。其测试精度高,失真度小。系统原理方框图如图1所示。

1系统硬件电路设计

本系统的硬件电路主要由输入信号倍频电路、AT89C51单片机、A/D转换器、D/A转换器、6116存储器及键盘/显示等电路构成。

1.1输入信号倍频电路

倍频电路由锁相环CC4046及双BCD同步加法计数器4518组成。4518作分频器用,实现720分频,其中,U3:A实现9分频,U2实现80分频。倍频电路中锁相环的输入信号是经过电压比较电路把工频信号变换成的方波信号。当分频器的输出信号(U2:A的6脚输出信号)与锁相环的输入信号fi相一致时,锁相环芯片U1锁存输出的信号频率为fo。假如输入信号频率fi=50Hz,则输出频率fo=36kHz。具体电路如图2所示。

该倍频信号的波形如图3所示,主要有两方面的用途,一是控制A/D转换的采样点数及采样的时间间隔(即一个周期采样720个点)。二是控制D/A输出数据的时间间隔,从而达到输入信号频率与输出信号频率一致。

1.2单片机系统主电路

本电路主要由单片机AT89C51、键盘/显示电路、模数转换器AD574A、数模转换器DAC0832、6116存储器等构成,具体电路如图5所示(键盘/显示电路和6116存储器等图中未画出)。键盘主要用来实现移相的具体数值(度)的设置,功能键包括设置键、数字键(“↑”、“→”)、复位键、运行键等五个键,最多可置720个0(720×0.5度=360度),因此可达到0~360度的相移。根据任意设定的相位数值,把相位及数据存储到队列(如图4所示)中的相应位置置0。显示用四位数码管实现,最低位为小数位,其余3位为整数位,可显示范围为0.5~360度。

A/D实现对波形数据(幅度)的采集、转换。A/D每采集一个点,就存入存储器的队列中。同样D/A借助单片机先从队列中读入一个数据,再由倍频信号fo来控制D/A输出数据的时间间隔,D/A的第一周期输出从“输出1”口输出,以后则从“输出2”口输出,对采集的720个数据循环输出,因此达到了移相的目的。

另外,因D/AC0832模/数芯片输出的波形存在毛刺,需要进行滤波,通过实验,在其输出端加一个1000p的电容就可以使这些毛剌基本消失,得到较平滑的波形。

2系统软件设计

整个系统软件的执行过程为:首先,通过键盘设置移相的数值,同时在显示器上显示出移相的度数;其次,启动A/D把转换结果存入队列,在A/D的转换过程中,D/A从队列中读出相应数据后D/A输出;第三,D/A不断循环输出,实现连续的移相后的工频信号。系统软件流程框图如图6所示。

3结束语

该数字移相器可对任意波形信号(如正弦波、三角波、锯齿波、方波等波形)进行任意相位的移相,具有测量精度高、跟踪速度快的特点,根据设定要求移相后所获得的输出波形与输入信号波形的幅度、频率逼近,即输出移相后波形的失真度较小。

责任编辑;zl

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)