1 引言

数字信号处理器(DSP)是一种适合于实现各种数字信号处理运算的微处理器,具有下列主要结构特点:(1)采用改进型哈佛(Harvard)结构,具有独立的程序总线和数据总线,可同时访问指令和数据空间,允许实际在程序存储器和数据存储器之间进行传输;(2)支持流水线处理,处理器对每条指令的 *** 作分为取指、译码、执行等几个阶段,在某一时刻同时对若干条指令进行不同阶段的处理;(3)片内含有专门的硬件乘法器,使乘法可以在单周期内完成;(4)特殊的指令结构和寻址方式,满足数字信号处理FFT、卷积等运算要求;(5)快速的指令周期,能够在每秒钟内处理数以千万次乃至数亿次定点或浮点运算;(6)大多设置了单独的DMA总线及其控制器,可以在基本不影响数字信号处理速度的情况下进行高速的并行数据传送。

由一片DSP加上存储器、模/数转换单元和外设接口就可以构成一个完整的控制系统,但这种方案要达到高速实时控制是不可行的。因为一个实时控制系统一般需要完成数据采集、模/数转换、分析计算、数/模转换、实时过程控制以及显示等任务,单靠一片DSP来完成这些工作势必会大大延长系统对控制对象的控制周期,从而影响整个系统的性能。所以我们添加一个CPU,负责数据采集、模/数转换、过程控制以及人机接口等任务,使DSP专注于系统控制算法的实现,充分利用它的高速数据处理能力。从性能价格比的角度出发,这个CPU采用8位的51系列单片机。这时,两个CPU之间的数据共享就成了一个重要的问题。

采用双口RAM(简称DRAM)是解决CPU之间的数据共享的有效办法。与串行通信相比,采用双口RAM不仅数据传输速度高,而且抗干扰性能好。在笔者实验室研制的电力有源滤波器中,选用了TI公司的第三代DSP芯片TMS320C32和51系列单片机89C52作为控制系统的CPU。两个CPU之间通过双口RAM CY7C133完成数据交换。但在实际使用过程中遇到了89C52 与双口RAM总线宽度不匹配的问题,需要进行接口电路的设计。

2 双口RAM CY7C133的内部结构和功能

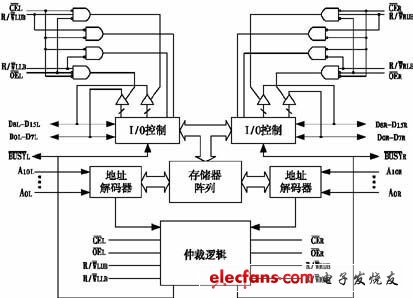

CY7C133是CYPRESS公司研制的高速2K×16CMOS双端口静态RAM,具有两套相互独立、完全对称的地址总线、数据总线和控制总线,采用68脚 PLCC封装形式,最大访问时间可以为25/35/55 ns。采用主从模式可以方便地将数据总线扩展成32位或更宽。各引脚的功能如表1所示,内部功能框图如图1所示。

CY7C133允许两个CPU同时读取任何存储单元(包括同时读同一地址单元),但不允许同时写或一读一写同一地址单元,否则就会发生错误。双口RAM中引入了仲裁逻辑(忙逻辑)电路来解决这个问题:当左右两端口同时写入或一读一写同一地址单元时,先稳定的地址端口通过仲裁逻辑电路优先读写,同时内部电路使另一个端口的信号有效,并在内部禁止对方访问,直到本端口 *** 作结束。BUSY信号可以作为中断源指明本次 *** 作非法。在主从模式中,主芯片的信号接上拉电阻作为输出,从芯片的信号作为写禁止输入。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)