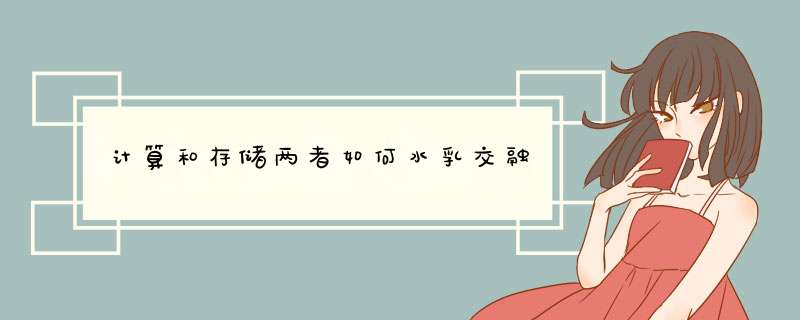

何能够让计算和Memory水乳交融,这个看起来的确是一个一石二鸟的想法。毕竟,作为CPU/GPU以及memory,从本质上大家都是门电路,没理由不在一起。在这里,就需要认真地再复习一下memory的类别了。

在易失的存储器中,主要就是SRAM和DRAM。两者都历史相对比较悠久的器件。而且,在大部分的心目中DRAM就是memory的缺省候选。对于DRAM来讲,有一篇神文值得安利。《What Every Programmer Should Know About Memory》[1],其中基本上介绍了程序员需要关心的Memory相关的信息,特别集中在DRAM上。当然,如果要写What Every Designer Should Know About Memory, 估计要关注SRAM了。

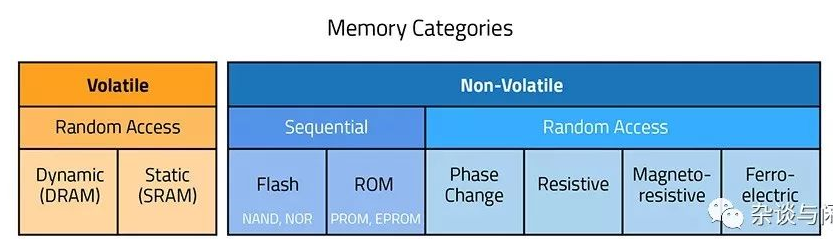

DRAM和SRAM的主要区别如下:

可以看出,SRAM相对于DRAM,需要更多的晶体管来实现。SRAM的好处是:

1. 不需要Refesh的电路,每个Cell的内容在写入之后,会一直保存到掉电为止。而DRAM则需要在10-100ms的时间级别进行Refresh。

2. SRAM的抗干扰能力要比DRAM强,这个也是那些晶体管的主要用处。

这里面没有提另一个关键的信息,就是功耗。对于一般的情况下,因为DRAM需要周期性地refresh,因此功耗比较大。但是SRAM自身功耗和主频的关系比较大,如果整个系统的时钟很高的话,SRAM的功耗可能会超过DRAM。

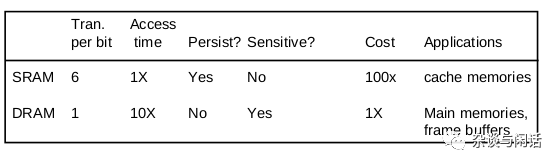

对于Memory来讲,定义它的主要性质的基本因素就是Cell,每一个Cell在RAM中代表一个Bit,但是更重要的是memory的array,任何的memory都不是单个cell的 *** 作,而是需要array level的 *** 作。

这个是memory cell 和memory array的示意图,可以看出,wordline 和bitline 是memory cell的基本概念,wordline 也是地址线,性质和enable类似,主要是来决定memory array中的一行cell可以被读取或者写入。当然,wordline的信息对应的地址是唯一的,而且在任意时间,只有一个workline处于High,也就是enable。

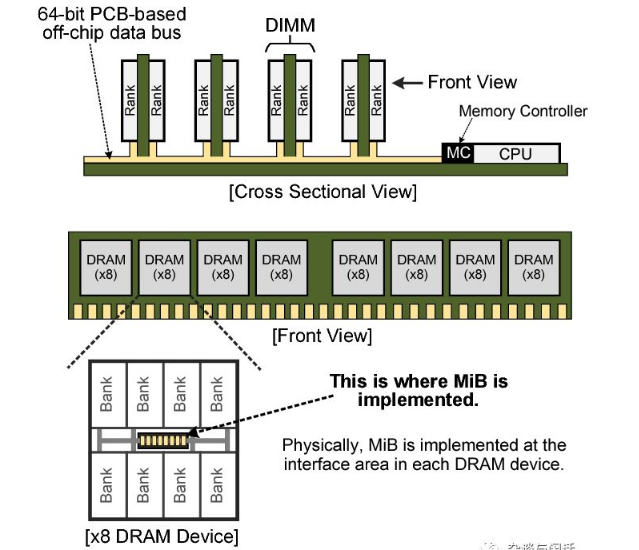

Bitline就是memory的真正位宽了,因为种种原因,内存的cell的word line 和bitline不没有做成完全的nxn的array,代表的地址的word line 总是要比bitline大很多,因此有了RAS和CAS的概念,先选ROW,再下一个周期选COL。对于Bitline,和目前的DDR相关的BANK的概念就是扩展Bitline常用的方式。

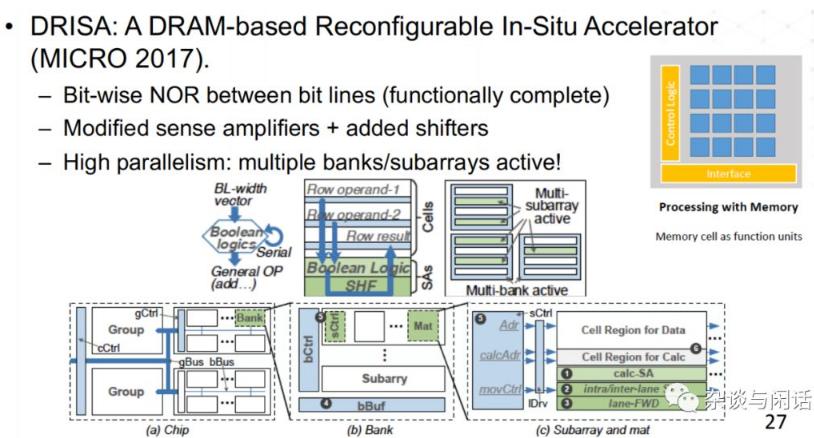

到这里,大家算是对于DRAM的memory array有了了解。切入正题,段博士的老板,也就是谢源教授在一个方向上的试探。[2]

有兴趣的自然自己可以去看原论文,这里只是贴上原文的总结。“

We compare four different DRISA designs and conclude that 1T1C -nor/mixed are the best choices. We then present a case study where

we evaluate CNN applicaTIons on DRISA. With the benefit of in-situ compuTIng, DRISA shows 8.8X speedup and 1.2Xbetter energy

effciency when compared with ASICs, and 7.7Xspeedup and 15Xbetter energy effciency than GPUs”。

个人认识是一个试探的原因有两个方面:

因为DRAM的商业壁垒太高,我们有基于Xilinx的FPGA做NVDIMM的客户,他们的商业模式都是自己做控制器和系统的开发,最后交DRAM厂家上产线生产组装。因为DRAM的高度垄断,因为任何基于DRAM方向的创新都需要他们的支持,目前来看,这些巨头对于这个方向并没有兴趣。而且其中Micron在2015-2016年在异构计算上的很多投资基本上都失败了。谢老师的合作伙伴Samsung电子,估计也是玩票性质。

和之前讲的计算和存储结合不同,这种方式需要对memory array做非常细致的拆解,而且处处定制。这个和GPU或者ASIC方案对比,实用性太差了。而且,相对与GPU 15X的性能功耗比,在2019大放异彩的以色列ASIC面前,基本上可以或略不济。

我曾在2017年的CNCC的会上,问谢老师,他的HBM在从提出到商业使用,基本上只花了不到10年的时间,这个真的很NB了。对于他的in-suite accelerator,他认为要花多久?谢老师很有风度的回避了这个问题。[3]

于是,这个革命的重任再次落到了NVM身上,诞生于1985年的NOR和NAND先完成了存储行业的革命,他们的近亲们现在在解决了random access的同时,希望利用array来解决计算问题。

目前来看,大家认为通过对于未来的可以支持Random access, byte address的新型非易失存储在架构上的优化来做到一石二鸟充满信心。段博士引用了几篇最近的论文,基本上都是基于MRAM[4]和ReRAM[5]的。MRAM在2018年的FMS上有几个相关的专题,但是从目前来看,MRAM的制程不能随工艺缩小,人家Samsung都在用1Y做DRAM了,他还在40nm。而ReRAM曾经是HP和Sandisk 的深度合作的基础,但是现在也是物是人非。

对于NVM和ML结合有很多不错的综述文章让大家上手。因为本作者才疏学浅,下一个关于ReRAM和MRAM相结合的文章目前没有时间表。作为补偿,给大家一个彩蛋,上上周在硅谷的中美半导体“Breaking the memory wall” [6],有兴趣的可以看看。

责任编辑:ct

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)