基于MATLAB与QUARTUS II的FIR滤波器设计与验证

1 引言

FIR数字滤波器能够满足滤波器对幅度和相位特性的严格要求,避免模拟滤波器的温漂和噪声等问题,具有精确的线性相位、易于硬件实现和系统稳定等优点,可广泛应用于现代电子通信系统。实际信号处理应用往往要求系统兼具实时性和灵活性,而现有设计方案(如DSP)则难以同时达到这两方面要求。而使用具有并行处理特性的FPGA实现FIR滤波器,具有很强的实时性和灵活性,因此为数字信号处理提供一种很好的解决方案。

在嵌入式导航计算机工程项目中,石英挠性加速度计的输出信号需进行数字滤波才能为导航计算机提供原始数据,为此需要设计一款FIR数字滤波器。这里使用MATLAB软件和Altera公司的FPGA开发软件QuartusⅡ进行FIR滤波器的设计仿真,该设计方案能够直观检验滤波器的设计效果,提高设计效率,缩短设计周期。

2 使用FIR IP Core设计滤波器

Altera公司提供的FIR Compiler是一个结合Altera FP-GA器件的FIR Filter Core,DSP Builder与FIR Compiler紧密结合。DSP Builder提供一个FIR Core的应用环境和仿真验证环境。而FIR滤波器设计实质上是确定能满足所要求的转移序列或脉冲响应的常数问题,设计方法主要有窗函数法、频率采样法和等波纹最佳逼近法等,这里采用窗函数法。

2.1 滤波器指标设计

FIR滤波器设计需达到以下指标:低通滤波,采样频率Fs为1 000 Hz,截止频率Fc为100 Hz,最小阻带衰减As为50dB,16阶滤波器,16位输入数据宽度,14位系数数据宽度。

2.2 利用FIR IP Core生成FIR模块

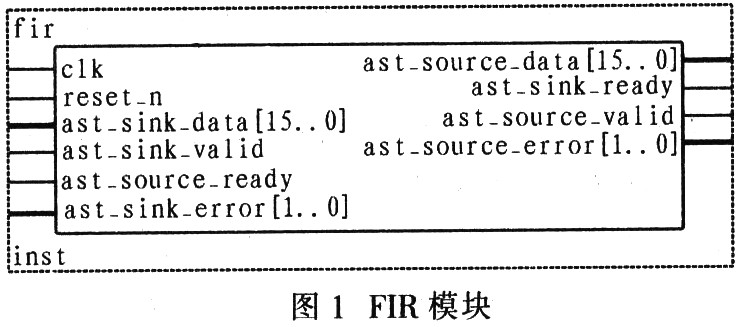

在FIR编译器中,将FIR滤波器设置为16阶低通滤波器,单速率采样。采样频率为1 000 Hz,截止频率为100 Hz,窗类型选择海明窗,然后生成系数并保存。滤波器系数的计算以所能达到最高精度为目的,计算出的滤波器系数未考虑有限字长效应,必须量化滤波器系数。由于在FPGA内要使用硬件实现滤波器,因此采用定点计算。按照指标要求设置参数,生成的FIR模块如图1所示。

3 验证方法的确定

基于FPGA的复杂DSP系统的调试验证是一项繁琐工作,采用传统的逻辑分析方法调试基于FPGA器件实现的设计几乎不可能。验证方法决定验证结果的准确性和验证工作量的大小。目前对基于FPGA的FIR数字滤波器的验证,通常采用输入一个信号序列(白噪声、多频谱混合信号等)作为激励,对滤波器的输出结果进行分析对照,判断滤波器是否符合设计要求。

4 利用Simulink检验滤波效果

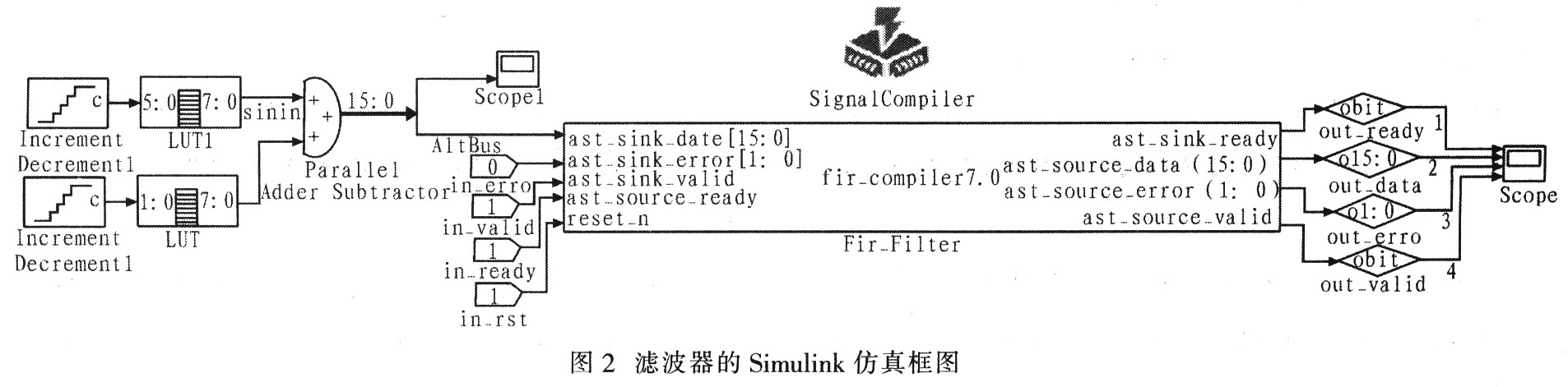

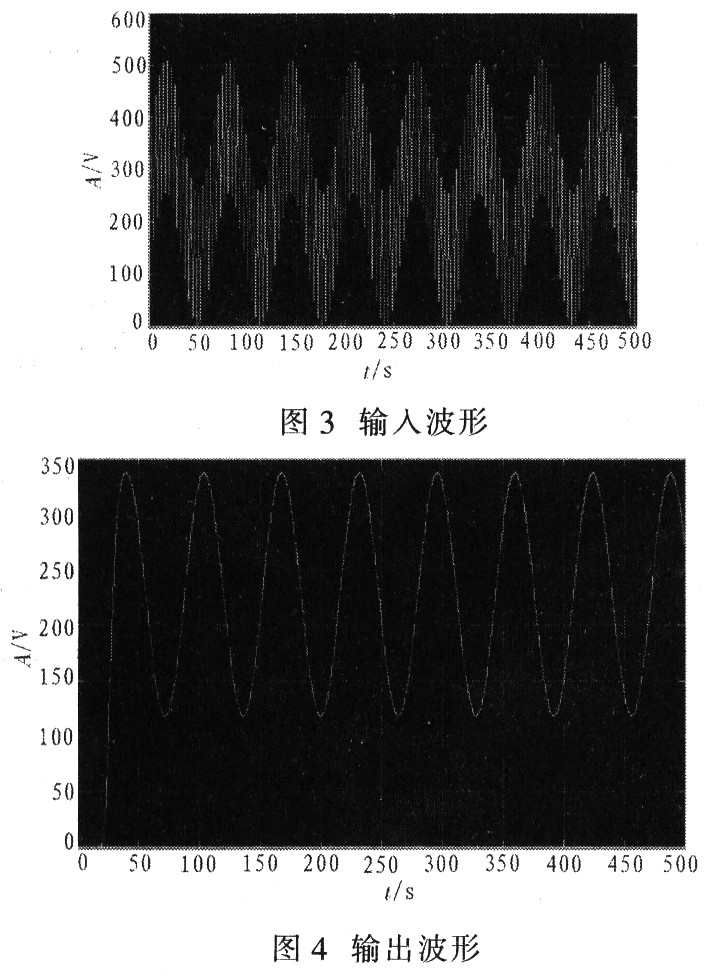

Simulink是MATLAB中一个专门用于对动态系统进行建模、仿真和分析的软件包。通过调用模块,可以构成仿真数字滤波器特性的结构框图。输入低频50 Hz和高频400 Hz的2个信号,利用所设计的滤波器进行滤波。建立仿真电路结构,导入前面所设计的FIR滤波器,如图2所示。

图3为输入波形在Simulink中Scopel的波形,图4为输出波形在Simulink中Scope的波形。比较图3和图4可看出,该FIR滤波器可有效滤除高频部分。因为在DSPbuilder中,输入正弦波形是通过查找表得到的每个周期256个点的量化值形式,故无物理单位,因此输出波形也是量化值形式。

5 使用ModelSim进行RTL级仿真

完成Simulink软件中的模型设计,仿真成功后,需要在ModelSim中仿真。因为Simulink中的仿真属于系统验证性质,是对mdl文件进行算法级仿真,而生成VHDL描述是RTL级,针对具体硬件结构。二者之间可能存在软件理解上的差异,转换后的VHDL代码实现可能与mdl模型描述的情况不完全相符,这就需要使用ModelSim进行RTL级功能仿真。图5所示是采用ModelSim仿真的结果,即低通滤波器的输出。可看出,与simulink中的仿真结果基本一致。

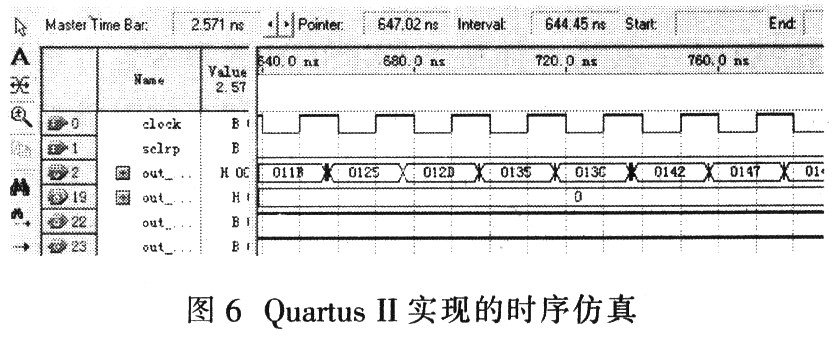

6 使用Quartus实现时序仿真

ModelSim完成的RTL级仿真只是功能仿真,其仿真结果并不能精确反映电路的全部硬件特性,因此,时序仿真仍十分重要。图6是用QuartusⅡ实现的时序仿真,可看出,时序仿真满足设计要求。

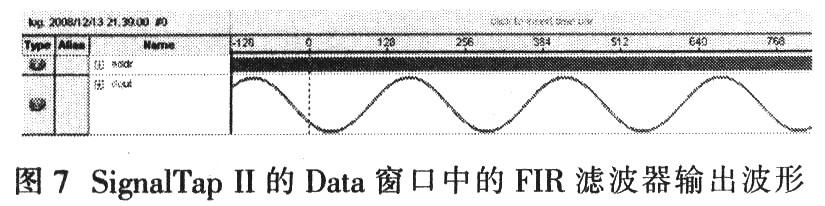

7 使用嵌入式逻辑分析仪SignalTap II测试

只进行工程软件仿真远远不够,还必须进行硬件仿真。signalTap II逻辑分析仪是Quartus II软件中集成的一个内部逻辑分析软件,使用它可以观察设计的内部信号波形,方便用户查找引起设计的缺陷。从Simulink建模仿真到Mod-elsim RTL仿真和Quartus II时序仿真,输入正弦波都是仿真信号,而不是实际信号源。在硬件实际运行时,可以从外部信号源接入器件内部或者在其内部存储正弦波数据。这里采用后者,即在顶层文件中引入LPM_ROM宏模块,在其中存入正弦波数据的mif文件(存储初始化文件),FIR滤波器模块直接从ROM中读取数据。实际测试发现,经过设计的低通滤波器后,高频信号被滤除,只有输出低频信号(标准的正弦波),滤波效果满足系统要求,嵌入式逻辑分析仪中的输出波形如图7所示。

8 结束语

本文在FPGA内利用DSPBuilder实现FIR数字低通滤波器,通过Simulink算法仿真和ModelSim进行RTL仿真,接着在Quartus中进行时序仿真。最后用嵌入式逻辑分析仪SignalTapII进行实际测试,结果证明采用该方法设计的FIR数字低通滤波器功能正确,性能良好,可以提高FIR滤波器的设计质量,加快设计进程,验证结果直观明了。随着各类数字信号处理的IP Cores的进一步完善,基于FPGA的DSP系统的应用会更加广泛。

200多个MATLAB经典教程和MATLAB论文请查看:matlab教程

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)