生产制造中的低功耗测试方法

受无线和高功效器件的普及以及提供“绿色”电子系统的需求驱动,设计师越来越多地采用低功率设计来应对越来越艰巨的功能性功耗挑战。直到最近,管理制造测试过程中的功率问题已经成为第二大备受业界关注的要求。但随着器件物理尺寸的不断缩小和电压门限的不断降低,越来越多的人认识到测试过程中过大的功耗会影响数字IC的可靠性,并导致电源引起的故障、过早失效,以及最终测试时发生错误问题。这些现象的发生要求制造测试采用特殊的电源管理和低功率设计技术。

功能模式与测试模式比较

多份研究表明,深亚微米器件的测试模式功耗要比功能模式高好几倍。虽然典型测试模式功耗极限通常是功能性功耗的2倍左右,但由于多种原因实际功耗要大得多。

例如,为了降低测试仪成本,有时会对多个模块同时进行测试,但在功能性 *** 作中,许多个模块同时工作的可能性并不大。扫描期间逻辑电路中的开关以及扫描/捕获期间的高开关速率也会产生较高的功耗。同样,转换测试波形中的快速捕获脉冲会导致有害的峰值电源脉冲,从而出现IR压降问题。另外,增加扫描转移循环的频率以缩短测试时间也会在测试仪上造成过高功耗。

测试功耗值不同于功能性功耗的其它原因还包括针对最坏情况下功能性功耗的现场测试要求,老化测试以及器件的高电压测试。所有这些 *** 作都会导致电压和温度的上升,从而对测试结果和器件的低功率电路造成潜在的负面影响。

在任何降低测试功耗的方法中,测试覆盖率影响必须要小,并且对自动测试波形生成(ATPG)工具和流程的影响要降低到最小程度。同样,也不应显著影响测试数据量和测试时间。另外,测试模式功耗降低得太多也可能导致电路受到的应力不够而影响测试质量,因此这种情况应避免。最后,采用的策略必须不影响物理设计因素,如面积、功率和功能时序,并且不影响开发进度。

DFT技术:Q输出选通和扫描划分

Q输出选通和低功率扫描划分(Scan ParTITIoning)就是两种常见的电源管理技术。在Q输出选通技术中,选通逻辑被智能地插在关键扫描触发器的Q输出端,以便尽量减少扫描转移期间组合电路中的开关活动。选通逻辑是由测试信号控制的,在捕捉周期和正常功能模式时不被激活。在扫描转移 *** 作期间,Q输出选通可以减少通过扫描触发器传播到组合逻辑的开关活动。重要的是只选通对扫描模式功耗降低有很大影响、但对设计中关键时序路径影响很小的寄存器。

扫描划分是另外一种管理测试功耗的可测性设计(DFT)技术。通过插入DFT逻辑,每条扫描链被分割成多个段,当测试数据从某个扫描段加载/卸载时,连接到所有其它段的时钟可以被关断以降低功耗。低功率扫描划分已经在一些商用设计中实现,如游戏系统中使用的CELL处理器。

降低测试功耗的另外一种相关DFT技术是数据选通,这种技术可以给目前不在进行测试的设计区域中的扫描链加载一个常数值。此时需要插入必要的测试点,以便给空闲链加载零值,从而减少开关活动,而工作链则加载来自测试仪来的数据。

DFT技术:禁止输出驱动器

输出驱动器在开关动作时的功耗通常要比内部逻辑大许多倍。尽量避免输出驱动器开关 *** 作对管理平均功率、即时功率和IR压降来说非常重要。它的主要思路是在任何测试模式时钟脉冲期间将所有三态输出驱动器保持在被禁(高阻)状态。这种方法可应用到捕捉和扫描转移时钟。这种方法可以在信号被证实时通过使用一个或多个控制输入信号强迫驱动器到高阻来实现。在扫描转移期间除了激活的扫描输出引脚外的所有驱动器应被禁止。

ATPG技术:具有功率意识的测试波形生成

除了DFT方法之外,商用化ATPG工具现在也考虑到了具有功率意识的测试波形生成功能。ATPG图案主要针对图案生成时的一个或一组故障。不会使控制状态发生冲突的波形可以被合并成统一的一个波形,这被称为波形压缩。当压缩完成时,一般不到3%的控制点会包含特定的值,这些值确定了针对目标故障的测试。这些确定的控制点称为关注位。剩余控制点(称为非关注位)可以用默认随机逻辑数填充。这些随机值偶尔可以用来测试不作为波形目标的故障。

这种非关注位的随机值填充将导致扫描期间发生约50%的设计扫描触发器开关动作。商用化ATPG工具提供的电源管理技术具有调整默认随机填充的波形生成功能。重复填充方法则重复最后关注位,直到遇到另外的关注位,从而可确保扫描转移加载期间的开关动作大大减少。无论使用哪种方法都可以获得同样的故障覆盖率。

例如,如果ATPG图案是0XXXX110XXXX11XXXX11,其中X代表非关注位,那么随机填充可能导致最终波形变成01010110101011010111,而重复填充变成01111110111111111111。随机填充有15反转,而重复填充只有3位反转,因此在扫描链转移期间反转率明显降低。为了避免开关动作减少得太多,另外一种方法是在对剩余位应用重复填充之前增加随机位来增加开关动作。一些ATPG工具提供对波形的更多自动化控制,可避免造成IC的应力不足。

电源器件测试

为了解决功能性 *** 作过程中的功耗问题,包括多路电压(MSV)和电源关闭(PSO)在内的许多架构级电源管理技术正得到越来越广泛的应用。这种技术可以提供高达80%的动态功率降低和几个数量级的漏电功率下降。这些设计具有多种电源模式,设计的不同区域(也称为域)可以处于不同的电源模式。

从DFT角度看,当内部扫描链、测试压缩、存储器BIST等测试结构被?入到这种设计中时,它们必须能在目标电源模式下工作。在以对应电源模式的测试模式测试芯片时,测试结构和实现与保持不同电源模式的控制器宏应该在测试仪上完全可控。

许多传统测试解决方案“不计较”这些低功率特性,并在所有域的电源接通条件下做测试。而在具有功率意识的测试方法中,设计的功能性电源模式被映射到ATPG测试波形。映射必须做到包含至少一个处于“开”状态的每个电源域的实例,这种状态允许以在用逻辑故障为目标,同时测试电源域隔离逻辑,并进行“开状态”验证。同样,还需要包含至少一个处于“关”状态的每个电源域的实例,用于验证和测试生成。

另外一个考虑因素是测试电源器件结构,包括电源控制器、电源开关和状态保持(SR)触发器,以及用于功能性电源管理的结构。在制造测试期间,必须对这些低功率器件中的缺陷进行精确建模和测试。例如,传统的结构化测试不足以测试支持电源关断和模式转换的逻辑,因为传统的ATPG和故障模型不足以解决处于断电中的逻辑问题。例如,在关断包含一个SR单元的域的电源后,由于SR单元不能保持最初加载的状态,SR单元可能无法正常工作。目前商用DFT和ATPG工具都支持具有功率器件意识的测试。

本文小结

制造测试期间的功耗潜在影响不能再被忽视了。许多IC设计团队的经验表明,好的工程规划、并行机制以及具有功率意识的DFT、ATPG和签字确认工具可以减轻测试低功率架构和元件过程中遇到的测试功率问题。本文重点介绍了几种实用的DFT和AFPG技术。随着低功率电子器件的快速发展,DFT和ATPG领域中将涌现出更多创新技术、工具和绝佳实用方法。

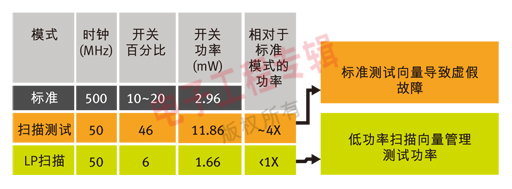

表1:使用测试波形电源管理技术的低功率扫描与传统扫描过程中开关功率的比较。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)