(文章来源:EET)

应对摩尔定律挑战的一个典型方案是异构集成和3D-IC。这也是现在比较流行的所谓more than Moore ( 超越摩尔定律),在封装层面的革新,是许多人认定延伸摩尔定律的一种可行方案。“赛灵思的异构集成已经做了很多年了。这张图我们也用了好几年了。”

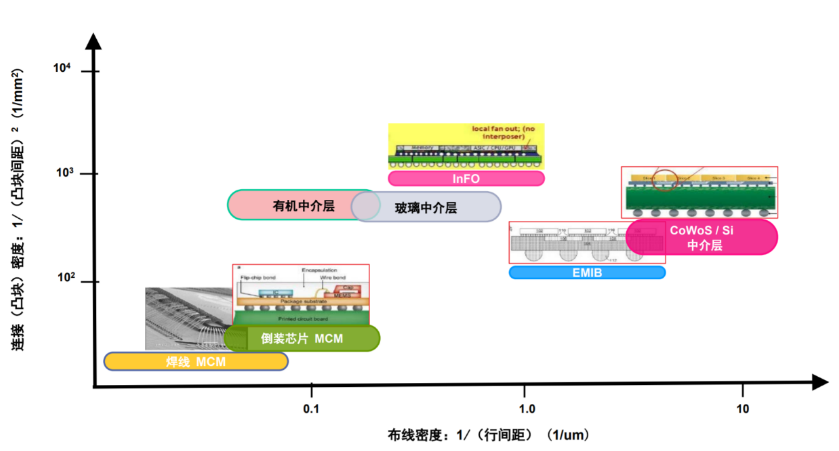

下面这张图就是典型的一些芯片堆叠方案。这些方案的核心思路,是一块芯片上包含不同die模块,每个die可以用不同的工艺来制造,这些die再通过各类封装技术集成到同一颗成品芯片内。不同芯片互联时,会有个中介层(interposer),位于封装基板(package substrate)以及die之间。Die与die的通讯通过interposer内的互联进行。所谓的“2.5D”封装也属于此类,典型如台积电的CoWoS、Intel的EMIB(EMIB有时也被认为是单独的一个类别,因为它是在substrate中加入了一层silicon bridge)。

在所谓的3D封装(acTIve interposer)中,interposer内部除了电路之外,也可以存在其他器件,典型的比如Intel的Foveros技术。3D-IC有时又指die堆叠,通过TSV一类技术在多层间实现互联,典型如索尼应用于图像传感器和ISP堆叠互联的Cu-Cu dielectric hybrid bonding,相比micro bump的密度增加将近百倍——我们在之前的文章中也提过。这类方案能够实现芯片制造和设计的效率最大化,这某种程度上是降低成本的一种方案;高速互联的3D封装,还能提升传输性能。这是它被称作摩尔定律延续的原因。

不同的异构封装方案,集成度是有差异的,这张图上,“越往右上角,功能就越强。左下角功能会弱一些,但成本低。”那么是否3D封装一定更好,或者上面这张图右上角就比左下角更好呢?用吴欣的话来说:“异构集成没有好与不好之分,只有适用和不适用。”“你的产品最适合哪个,就去选哪个。”

“我们2011做的第一颗异构集成芯片是V2000T。当时,如果我们不用异构集成的话,要做这么大的芯片,很大。”吴欣用手稍稍比划了一下,“这么大的芯片,一片12寸的晶圆(wafer)在比较早期这样的芯片的良率只是两个。因为良率与面积的关系不呈线性而是呈指数关系。如果这颗芯片切分成四块,每片wafer就能有100个good dies,每四个组成一颗芯片,就有25颗芯片,考虑到额外的一些损失:哪怕损失一半,那也有12个半。相比不做异构集成,有6倍的益处。对客户来说,也就不需要花6倍的价钱去买。”

但从经济方面考虑,这种收益也并不是绝对的。“再举个例子,2014年我们知道5G是个方向,针对5G我们当时第一次把数模转换和可编程模块放在一起。我们做了一个65nm的ADC/DAC (数模转换),加上我们自己的可编程模块是28nm,两个异构集成在一起。客户说产品的确不错,但无法满足价格考量。所以一直到3年以后,工艺进步至16nm,我们最后还是把它集成在了一个单独的芯片上,monolithic (单芯片),造价也终于可接受了。”吴欣所说的这个例子,应该是指现如今赛灵思正火的融数字与模拟为一体的RFSoC 产品系列。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)