对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步复位/置位资源和采用内部复位。上述方法可有效提高FPGA复位的可靠性。

对FPGA芯片而言,在给芯片加电工作前,芯片内部各个节点电位的变化情况均不确定、不可控,而这种不确定且不可控的情况会使芯片在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输出关联的系统产生不良影响,FPGA上电后要进行复位,且为了消除电源开关过程中引起的抖动影响,复位信号需在电源稳定后经过一定的延时才能撤销,FPGA的复位信号需保证正确、稳定、可靠。

在FPGA的设计中,多数情况下复位电路的功能虽能够正常完成,但电路并未得到精确合理的设计,仍存在可靠性设计缺陷。为确保系统复位的可靠性,有必要对FPGA复位的可靠性设计方法进行研究。

1复位设计方法分类

复位的目的是在仿真时将设计强制定位在一个可知状态,合理选择复位方式是电路设计的关键。根据与系统时钟域的关系,复位电路可分为同步复位和异步复位。同步复位是指复位信号只在时钟沿到来时,才有效。否则,无法完成对系统的复位工作。异步复位是指无论时钟沿是否到来,只要复位信号有效,使对系统进行复位。

根据是否存在外部复位端口,复位电路又可分为外部复位和内部复位。外部复位是指复位信号主要来自外部引脚的输入,如复位按钮、电源模块输出等。内部复位信号则是主要由FPGA内部电路产生。

2复位设计方法的比较

2.1同步复位与异步复位

2.2.1同步复位

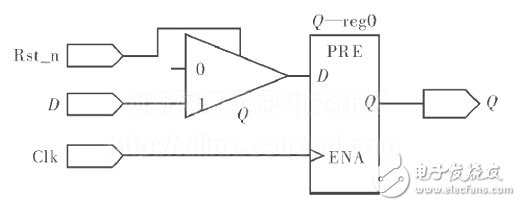

指定同步复位时,always的敏感表中仅有一个时钟沿信号,只有当时钟沿采集到同步复位的有效电平时,才会在时钟沿到达时刻进行复位 *** 作。若目标器件或可用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可直接调用同步复位端。然而多数目标器件的触发器本身并不包含同步复位端口,需使复位信号与输入信号组成某种组合逻辑,然后将其输入到寄存器的输入端。为了提高复位电路的优先级,通常在电路描述时使用带有优先级的if…else结构,复位电路在第一个if下描述,其他电路在else或else…if分支中描述。复位电路综合后的RTL图如图1所示。

图1同步复位电路图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)