现在有很多电路(例如IDT的可编程时钟发生器)为了减少配置输入引脚数目(亦可缩小电路封装尺寸),输入引脚除了常规的高(“1”)、低(“0”)2种电平状态外,还增加了第三种状态:悬空(“Z”),IDT称作“M”电平。这样,2个输入引脚就可给出9种配置:00、01、10、11、0M、1M、M0、M1、MM,比常规两电平的4种配置多出6种。

实际应用中,如果用户希望在自己设计的电路(如:FPGA、MCU等)增加三电平输入,检测方法有三种:

1、对于FPGA,方法很简单,使用下述VHDL语句即可:

if (input=’0’) rhen

//低电平

elsif (input=’1’)then

//高电平

else

//悬空

也可使用case语句直接判断:”00”、”01”、”0Z” 、“1Z”等。

2、采用类似FPGA或DSP的弱上拉加下拉电阻(如100K)方法,当输入接GND、VCC或悬空时,输入内部的电压则为0V、VCC、1/2VCC,可以采用双门槛比较器或AD转换器判出1/2VCC状态。

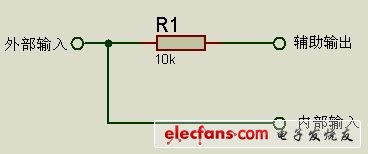

3、上述第2种方法判断1/2VCC电平状态比较麻烦,可采用下述更简便的判断方法:

如上图所示,电路内部增加一个串联10K电阻到外部输入端的“辅助输出”,当“辅助输出”输出高低变化电平时,“内部输入”检测到这种变化,则“外部输入”是悬空的,如不变,则“外部输入”是固定高、低电平。

值得注意一点的是,对于三电平输入引脚,一般外部不能再加上拉或下拉电阻,而是直接接VCC、 GND或悬空。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)