一、实验目的

熟悉QuartusⅡ的VHDL文本设计过程,学习简单组合逻辑电路的设计、仿真和测试方法。

二、实验内容

1. 基本命题

完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤。最后在实验系统上进行硬件测试,验证本项设计的功能。

2. 扩展命题

将设计的2选1多路选择器看成是一个元件mux21a,利用元件例化语句设计能够满足图3-1所示仿真波形的逻辑功能的双2选1多路选择器。

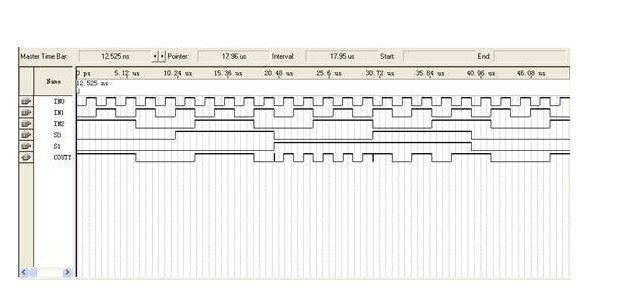

图3-1 仿真波形

三、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

四、实验

将实验原理、设计过程、仿真步骤、仿真波形和分析结果、硬件测试实验结果写进实验报告。

2选1多路选择器设计

① 实验原理

由数电知识可知,2选1多路选择器由2个数据输入口(IN0,IN1),1个数据选择端(S1),一个输出口(COUTY)构成。本程序通过判断数据选择端(S1)的取值,将对应的数据输入口(IN0或IN1)输出。

② 程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY mux21a IS

PORT ( IN0,IN1,S1:in std_logic;

COUTY : OUT STD_LOGIC);

END mux21a;

ARCHITECTURE behav OF mux21a IS

BEGIN

COUTY《=IN0 when S1=‘0’ ELSE IN1;

END behav;

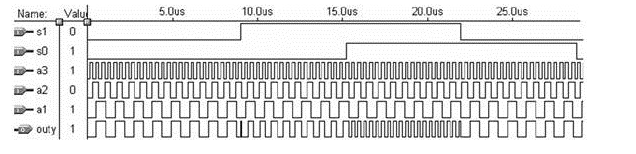

③ mux21a仿真波形图

为了使仿真结果更为直观,我们将IN0设为高电平,IN1设为低电平。

图1 mux21a仿真波形图

由图1可知,我们可知当S1处于高电平时,COUNT输出IN1;反之,输出IN0.所以所设计的实验能够满足要求。

双2选1多路选择器

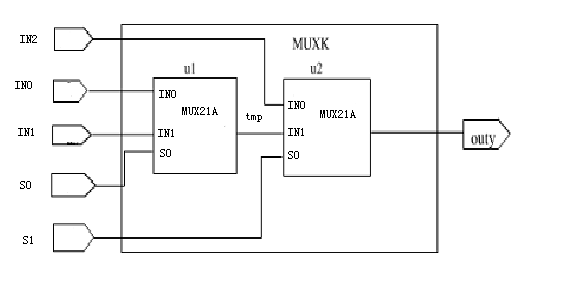

① 实验原理

本实验中直接利用上题的mux21a。由上题可知,mux21a由2个数据输入口(IN0,IN1),1个数据选择端(S1),一个输出口(COUTY)构成。设有两个mux21a,分别为U1和U2。为了充分利用U1和U2的数据选择端,我们将U1的输出口(COUNT)接到U2的输入口IN0,这样U2通过自身的选择端(S1)就可以选择U1的输出或则自己IN0的输入数据,实现2选1选择器到双2选1多路选择器的扩展。(如图2所示)

图2 双二选一多路选择器

② 程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY dmux21a IS

PORT ( IN0,IN1,IN2,S0,S1:in STD_LOGIC;

COUTY : OUT STD_LOGIC);

END dmux21a;

ARCHITECTURE BHV OF dmux21a IS

COMPONENT MUX21A

PORT(IN0,IN1,S1:IN STD_LOGIC;

COUTY :OUT STD_LOGIC);

END COMPONENT;

SIGNAL tmp : STD_LOGIC;

BEGIN

u1 : MUX21A PORT MAP(IN0, IN1, S0, tmp);

u2 : MUX21A PORT MAP(IN2, tmp, S1, COUTY);

END BHV;

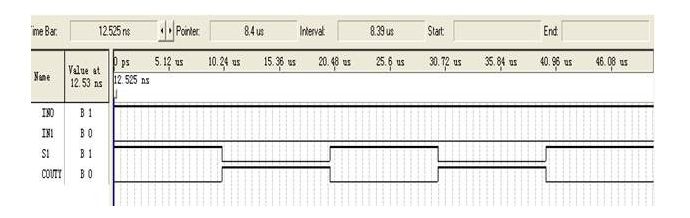

③ dmux21a 仿真波形图

图3dmux21a仿真波形图

波形图预测:当S1=0时输出IN2的波形;当S1=1,S0=1,输出IN1的波形;当S1=1,S0=0,输出IN0的波形。

由波形图可知,方针结果与预测结果一致。

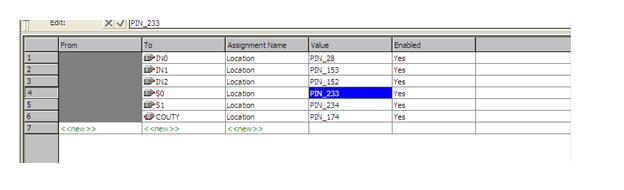

(2)进行本实验引脚锁定时,建议选择实验模式5(No.5),用键1(PIO0)控制端s0;用键2(PIO1)控制端s1;a3、a2、a1分别接clock5、clock0和clock2;输出信号y接扬声器spkert。通过短路帽选择clock0接256Hz信号,clock5接1024kHz信号,clock2接8kHz信号。最后进行编辑、下载和硬件测试实验(通过选择键1、键2、控制s0、s1,可使扬声器输出不同音调)。

表1-1 dmux21a在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

端口名称端口符号GWAC6板输入输出元件GWAC6板接口目标器件引脚备注

控制端s0s0键1PIO0233模式No.5

控制端s1S1键2PIO1234

输入信号3IN2clock5clock5152

输入信号2IN1Clock0Clock0153

输入信号1IN0Clock2Clock228

扬声器y扬声器SPEAKER174

如表1所示完成元件dmux21a与实验板引脚的绑定。如图4所示

图4 dmux21a与实验板引脚的绑定

五、实验思考题

比较图形编辑输入与文本编辑输入的主要差别,谈谈例化语句的作用及应用时应注意的问题。

1、比较图形编辑输入与文本编辑输入的主要差别

使用图形编辑法的话,我们需要对逻辑运算与硬件结构对应起来,也就是要懂得将逻辑运算转化成硬件电路,这需要有较为扎实的硬件功底。使用文本编辑输入的话,我们只需要懂得用VHDL表达逻辑运算,而不必关心硬件电路的组成,这可以减轻很多硬件设计方面的功夫(接线,选用元器件等)。

2、例化语句的作用及应用时应注意的问题

1) 例化语句的作用是:引入另一个已经设计好的组件。

2) 应用时应注意的问题:

① 要记得将原先已经设计好的原件放在工程底下。对于本体来说是mux21a。

② 要将引入的元件与顶级元件的引脚一一匹配,有需要的话,使用信号(SINGAL)进行消息的传递。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)