安迪•乔力是一名高级应用程序顾问——该程序即Synopsys全球产品线领导品牌,基于FPGA的原型设计。安迪已从事FPGA技术研发25年多。最近,他又开始向客户提供支持,支持他们建立在Synopsys HAPS平台上的复杂CPU SoC和GPU IP原型设计需求,并同时在全球范围内对嵌入在用户程序中相同SoC和GPU IP的开发提供支持。

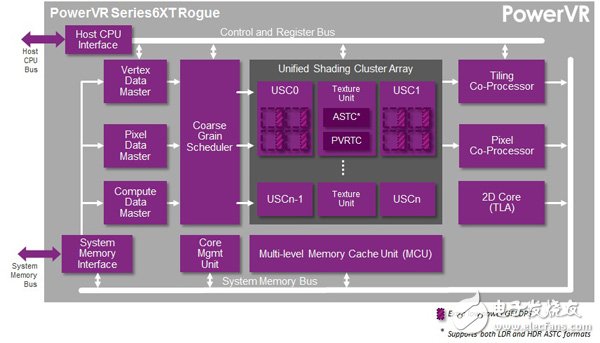

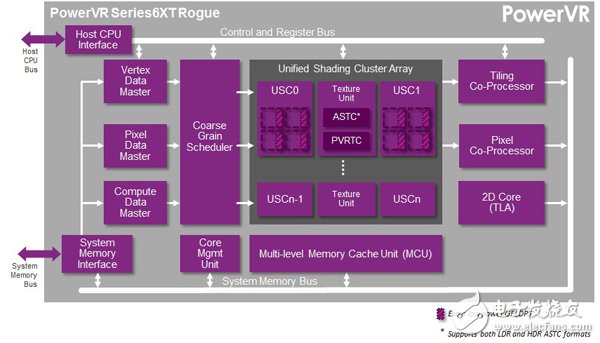

PowerVR Rogue GPU的建立基于效率市场领先的原则,这使过去几代图像处理器的性能得以显著提高。为了获得高性能,GPU架构利用强大的并行处理能力来处理高要求的图像和计算任务。为获得高性能而配置GPU IP时,设计团队面临的是多重的挑战。他们需将复杂、高门数的设计融入单一FPGA有限的空间里。考虑到Series6、Series6XE 和Series6XT系列的可扩展性(从半个到八个集群),在尝试测试这些复杂设备时却面临着更多的挑战。

PowerVR Series6XT GPU的规模是从两个集群到八个集群。由于其它选择(即制造测试芯片)的过程变得越来越昂贵且耗时,Synopsys和ImaginaTIon便合作打造更具活力基于FPGA的原型设计结构。由此,使用多个FPGA甚至是最大的PowerVR GPU建模的新型优化流程便得以问世。下述将具体展示获得这一建树的经历。

GPU原型设计需求

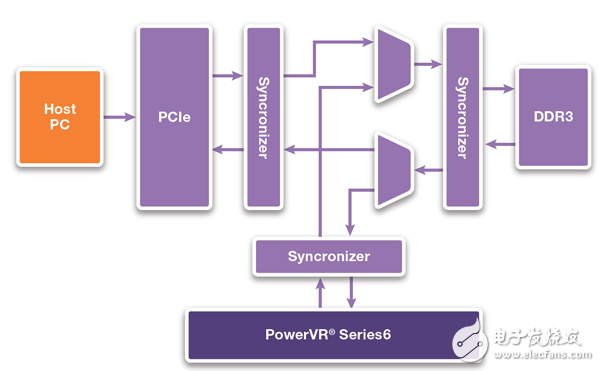

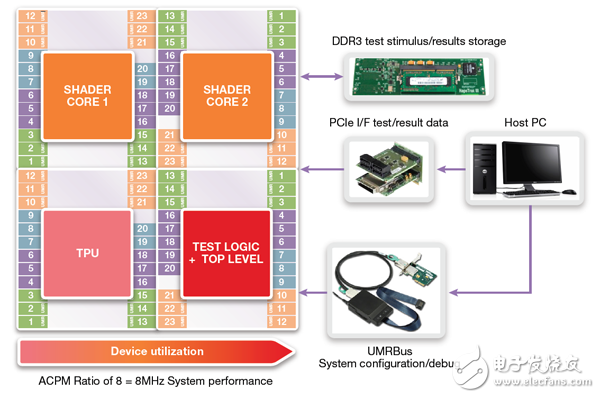

Synopsys所做的第一步是启动一个概念验证项目。这个项目为ImaginaTIon的PowerVR Series6 GPU展示了基于FPGA的原型设计。原型设计环境包括一个独立回归测试的顶层测试架构。试架构通过PCIe端口和使用DDR3存储接口的存储测试激励和结果连接至PC主机。这使得测试团队得以控制和分析GPU,并通过Universal MulTI-Resource BUS (UMRBus)对系统进行配置且从PC主机访问测试和结果数据。

支持回归测试的顶层测试架构

团队为包含多重FPGA的Synopsys HAPS-70 S48原型设计系统的实施进行手动的设计区分,获得了几个MHz的时钟速度。在该系统上将实施7000个回归测试——所有测试都不需要测试芯片。我们不仅仅区分衍生设计(甚至比Series6 GPU更大的设备),还创建了额外的测试逻辑和充足的性能,以支持视频输出。这可通过使用ProtoCompiler完成。ProtoCompiler是Synopsys第二代FPGA自动化区分工具。ProtoCompiler旨在将启动所需的时间和工作量最小化,再为IP验证和软件开发部署Synopsys HAPS系列系统。它结合了自动化特性,用于设计规划、逻辑综合、调试和连接到其它验证环境如Synopsys VCS和ZeBu。原型软件与HAPS系列紧密结合,以提供系统性能。

PowerVR Series6和Series6XT原型的成功意味着ImaginaTIon设计团队在将新型GPU引入市场时很少依赖测试芯片的使用。对原型的早期访问可确保系统验证、早期的软件开发并简化软硬件集成。

Synopsys HAPS-70中的PowerVR Series6 GPU

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)