为给DSP、ASIC、FPGA和微处理器的负载点供电而引起的电压输入轨数目的增多使得电源设计更加具有挑战性。特别是由于系统功率和工作频率要求的增加,造成基础设施、工业和工厂自动化设备对噪声和其他不可预测事件更加敏感。例如,系统启动时的错误输入电压会引起系统闩锁、可靠性问题甚至系统故障。

本文讨论如何针对FPGA或微处理器配置各种电压输出跟踪和时序控制选项,来帮助实现灵敏多电源轨系统的正确启动和关断。我们还将分析比率和同步跟踪设置,用于防止FPGA的内置静电放电二极管 (ESD) 在上升和下降输出期间偏压或过度受压。这些配置可显著提升系统可靠性,这对保证广泛的基础设施系统和工厂车间工业设备的生产率和正常运行时间非常重要。

系统配置

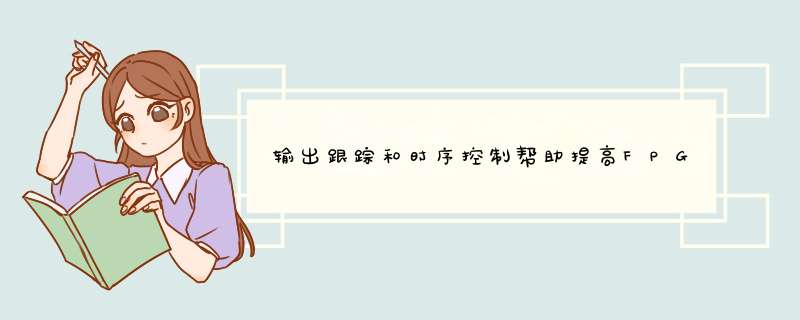

图1显示了针对FPGA的典型应用电路配置。从3.3V最高输入轨到2.5V第二输入轨,我们发现一组背对背ESD二极管配置充当内部保护电路。另一组背对背ESD二极管配置是从第二输入轨至第三输入轨。

图1. FPGA输入框图

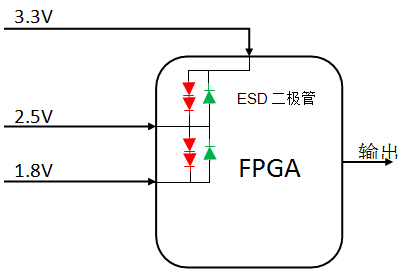

我们假设一种最高输入轨(在这个例子中为3.3V)最先启动的情况。然后,其将2.5V输出轨预偏置至约1.9V,将1.8V轨预偏置至1.2V。类似地,如果1.8V轨首先启动,则其对2.5V和3.3V轨进行预偏压。在任一种情况下,ESD二极管都必须在启动期间导电。图2显示了3.3V输入轨的电压信号及其在启动前发送至2.5V轨的信号。流经ESD二极管的充电电流取决于启动压摆率、2.5V输出电容以及任何负载。以1.8V输出轨执行相同的启动情景会显示类似的电压信号。

图2. 3.3V和2.5V预偏置的启动波形

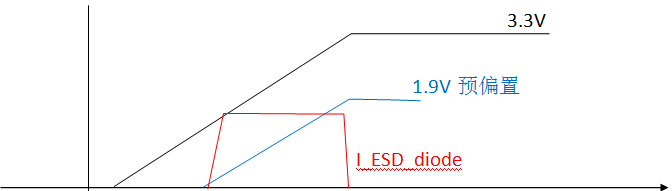

每当ESD二极管导电时,其可靠性就会下降。图3显示了当2.5V输入源未设定为带有预偏置启动功能时3.3V和2.5V轨会发生什么情况。可以看到,FPGA的内置ESD二极管在2.5V轨启动时受到压力。因此,使用带有预偏置启动功能的电源可避免该问题和防止系统可能出现的闩锁。正确的配置降压稳压器的输出电压跟踪功能可确保所有系统电源轨一起正确软启动,并防止ESD二极管导电。这个简单步骤可提升系统可靠性和避免任何意外的系统电源闩锁。

图3. 3.3V和2.5V的启动波形

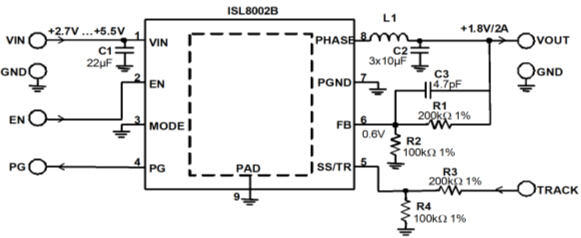

图4显示了输入电压范围为2.7V - 5.5V的2A DC/DC转换器的典型应用电路。只使用了几个外围元件,包括需要的电阻、电容和电感。转换器集成了补偿电路和功率MOSFET来保证设计可靠性、最小元件数目和可达95%的高效率。

图4. ISL8002B的典型应用原理图

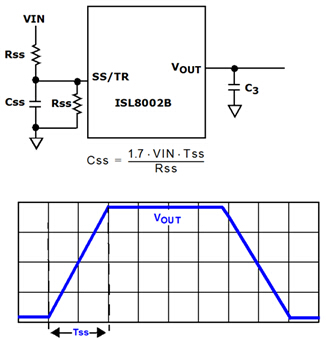

转换器的引脚5同时提供软启动 (SS) 和输出跟踪 (TR) 功能。当该引脚连接高电平时,软启动时间在内部设置为1ms。但是,使用外围元件可实现各种软启动方案。图5显示了如何使用SS/TR功能来编程外部软启动时间。

图5. 外部软启动配置

通过设置软启动电阻RSS和电容CSS可调整软启动时间。相应的近似关系如式1所示:

式1

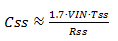

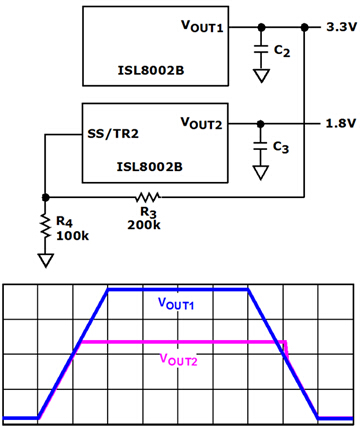

另外还可配置该软启动功能来跟踪其他输出。图6显示了Vout1-Vout2的比率跟踪配置。

图6. Vout1-Vout2的比率跟踪

此外,还可以通过将两个SS/TR连接到一起来使两个输出电压同时上升。类似地,关断功能还可相互进行比率跟踪,如同式1中描述的软启动时间一样。

同步跟踪配置如图7所示。只需添加一个电阻分压器,其比率与其在反馈回路中的输出电压感测分压器的比率相同。在此情况下,所有输出电压按照主轨以相同的电压和斜率上升。通常,所有其他输出轨应当跟踪最高电压轨。然后,每个输出将在达到其稳定点后分支。通过很好地控制所有输出轨的启动和关断,可防止图1的内置ESD二极管导电或正向偏置。最重要的是,该设计技术可防止系统可靠性下降、闩锁以及更坏的情况:系统故障。

图7. Vout1 - Vout2的同步跟踪

结束语

诸如ISL8002B等集成FET式步降稳压器,为加电和断电期间的电压跟踪提供了大量易于使用的解决方案。任何系统电压跟踪需求几乎都可以使用本文讨论的电路进行配置。这些配置不限于两个稳压器,因为它们能用于系统中的任何数量的电压轨。只需要将所有SS/TR引脚连接到一起即可进行比率跟踪。另外还可使用电阻分压器来对系统进行同步跟踪编程。无论是比率跟踪还是同步跟踪方法均可防止ESD二极管承受不必要的压力,从而提高系统的整体可靠性。

作者简介

Tu Bui是Intersil公司的工业与基础设施产品应用工程经理。他负责开关稳压器产品研发及所有相关客户应用支持工作。在加入Intersil之前,Bui先生是AT&T贝尔实验室的Technical Staff Design Engineer成员,在那里他研发和推出了超过20种世界级产品及产品族。Bui先生拥有亚利桑那大学的电气工程学士学位 (BSEE) 和南方卫理公会大学的工程管理硕士学位。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)