0 引言

随着电力电子技术的不断发展以及工业用电设备对电能质量需求的不断提高,越来越多的复杂拓扑结构、大容量系统、高安全稳定性的电力电子设备得到研究并应用到众多实际工程实践。针对多种电力电子拓扑结构不同工程应用实际,其相应的控制、保护系统同样越来越趋于复杂化和多样化。先进处理器的控制系统是现代电力电子设备的核心部件[1-3],以 DSP 为代表的传统处理器控制系统在中低压电力电子设备控制和保护中已有广泛的应用,并且取得了良好的控制效果。但在高压大功率电力电子设备控制系统的应用上,传统 DSP 控制器还存在不足。首先是 AD 采样通道和 PWM 信号输出通道数量有限,难以满足拓扑结构复杂的大功率电力电子设备的检测和控制要求;其次是由于 DSP 芯片在运行中复位在所难免,复位期间无法对电力电子设备进行有效控制与保护;最后是传统 DSP 控制器无法对输出 PWM 信号进行有效检测与识别,且 PWM 信号出错后无法立即采取闭锁等保护措施。

然而,DSP 作为专门用于数字信号处理的微处理器,在条件进程、复杂的多算法计算方面具有独特优势[4-5],可以在控制系统中增加 FPGA 和 CPLD 弥补其不足[6-8]。FPGA 具有强大的并行处理能力和多时钟频率等优点[9-10], 能完成复杂的时序逻辑设计,实现高速、高频的 AD 采样和 PWM 信号输出控制及通道扩展[11-12]。而 CPLD 则可高速检测 PWM 输出信号并且在 PWM 信号出错故障情况下瞬时启动系统闭锁功能,提高系统控制的可靠性[13-14]。因此,将 DSP、FPGA 和 CPLD 高效结合并以此来设计控制系统,对高压大功率电力电子设备进行可靠、全面的控制和保护具有重要意义。

基于上述背景,本文提出一套适用于高压大功率电力电子设备通用型控制控制器。该控制器采用主控制板与其他插件板相分隔的分板块硬件系统结构,结合了 DSP、FPGA、CPLD 各自性能特点的同时兼顾了通用性;提出了多时间尺度控保融合的软件设计方案,分别从系统级、器件级、信号级三个层面实现对设备的控制和保护,以满足众多高压大功率电力电子设备对控制与保护的要求。

1 系统整体方案设计

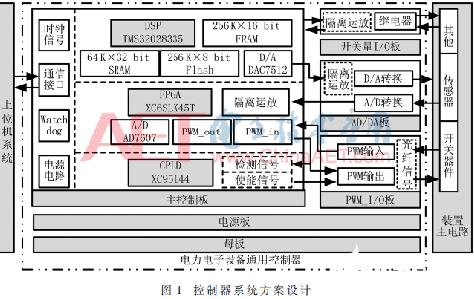

针对高压大功率电力电子设备的安全可靠性要求较高、控制算法较为复杂、控制与检测信号量较多等特点,本文以 DSP+FPGA+CPLD 为核心,结合高性能外围器件和高速接口,设计了一种主控制器与外围插件板分离的硬件方案。

该系统集高速算法运行、快速输入输出接口、多时间尺度控保融合于一体,对不同结构和功率等级电力电子装置的算法执行、继电保护配置都有较强的适应性。基于 DSP+FPGA+CPLD 的电力电子设备通用控制器系统方案如图 1 所示。

2 系统硬件设计方案

2.1 系统主要器件选型

2.2 系统板块功能介绍

由图 1 可知,控制器主要分为包含 DSP、FPGA 和 CPLD 的主控制板,PWM 输入和输出的 PWM_I/O 板,A/D 转换和 D/A 转换的 AD/DA 板,开关量输入和输出的开关量 I/O 板,包含多个开关电源模块的电源板,以及负责上述各个板块间连接的母板几部分。其中,各个功能板块电路模块设计固定,除主控制板、电源板和母板外,PWM_I/O 板、AD/DA 板、开关量 I/O 板均可根据控制对象需求进行板块数量增加。

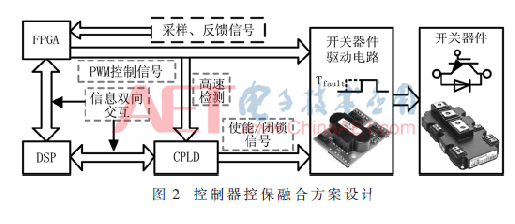

主控制板为整个控制器核心。其中 DSP 及其相应外围电路实现复杂控制算法执行、事件记录、与上位机通信、D/A 转换输出以及部分开关量输入输出等核心控制与系统级保护功能;FPGA 及其相应外围电路主要控制高速 A/D 采样与转换、PWM 信号的发生以及 PWM 信号的输出与接收等器件级控制功能;CPLD 及其相应外围电路完成对 FPGA 产生的 PWM 信号的高速检测,并在 PWM 信号输出正确时输出使能信号完成 PWM 信号向开关器件的传输,否则闭锁 PWM 信号输出,并向 FPGA 和 DSP 进行反馈,FPGA 停止 PWM 信号发生和输出,DSP 进行事件记录并输出告警信号。主控制板是整个控制器实现对电力电子设备的多时间尺度控保融合的核心板块。图 2 所示为控制器控保融合方案设计。

PWM_I/O 板是控制器输出核心控制信号的转换通道。其中光纤发射器 HFBR1528T 及其相应外围电路完成将 FPGA 输出的 PWM 电信号转换成 PWM 光信号,并在收到输出使能信号后向开关器件驱动电路输出 PWM 光信号;光纤接收器 HFBR2528R 及其外围电路则负责将接收到光信号转换成电信号,并输入值 FPGA。PWM_I/O 板是控制器实现 PWM 信号的输出、检测以及故障闭锁的关键板块。

AD/DA 板为控制器关键控制信号与反馈信号的变换通道。其中由二极管、电阻、电容、放大器构成的滤波及运放电路实现对外部传感器输入的电压信号的滤波与放大,将带采样信号变换为 0~±10 V 的电压信号,并输入至主控制板;同样由二极管、电阻、电容、放大器构成的运放电路实现对主控制板产生的小功率模拟信号进行放大并输出。AD/DA 板是控制器实现闭环控制的关键环节。

开关量 I/O 板是控制器与紧急停机、设备状态指示灯等外部开关量相连接的通道。当外部开关量信号输入控制器时,经板上 TLP521 光电隔离模块后转换小电量信号输入主控制板;当控制器开关量信号输出时,经板上继电器模块控制外部器件。

电源板是将外部输入 220 V AC 电源转换成其他板块所需要的 5 V、±15 V、24 V 等直流电源的模块。外部 220 V AC 电源输入控制器时,经板上双节电磁干扰(ElectromagneTIc Interference,EMI)滤波器滤除高次谐波后,输入给板上各个开关电源模块转换成相应的直流电源。

母板是将上述各个板块进行有效连接的板块。母板与其他板块之间采用 96 pin 欧式连接器进行连接。母板的存在使得当控制器应用于需求不同的电力电子设备时只需重新设计母板进行直接扩展 PWM_I/O 板、AD/DA 板、开关量 I/O 板 *** 作。

3 系统软件设计方案

控制器系统根据 DSP、FPGA、CPLD 各自特点,采用了基于 DSP 的毫秒级控保方案、基于 FPGA 的微秒级控保方案和基于 CPLD 的纳秒级保护方案相融合的多时间尺度一体化软件设计。

3.1 DSP 软件设计

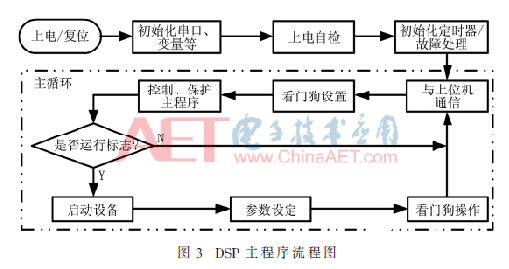

DSP 软件主要完成电力电子设备核心算法运算、与上位机通信以及事件记录等功能,其程序可分为主程序部分和定时中断服务子程序部分。

主程序包括初始化和主循环两大部分。控制器上电或复位后,首先执行串口和数组初始化程序,然后进行开关量自检和 AD 通道的自检。若自检正常则进行初始化定时器 *** 作,否则执行故障处理程序,并输出告警信号。初始化完成后进入主循环程序,主要包括与上位机通信、看门狗设置、等待设备运行等流程。DSP 软件主程序流程如图 3 所示。

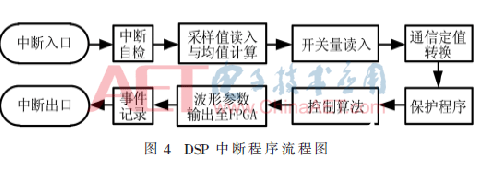

中断程序主要完成中断自检、对来自 FPGA 的 AD 采样值读入与平均值计算、开关量读入、通信定值转换、保护程序执行、控制算法运算、波形参数(占空比或正弦波)输出以及事件记录。中断程序的执行周期可根据实际设备需求进行修改。DSP 中断程序流程如图 4 所示。

3.2 FPGA 软件设计

FPGA 软件主要为基于多时钟频率下并行处理的高速 AD 采样控制和 PWM 信号的输出全数字化实现。

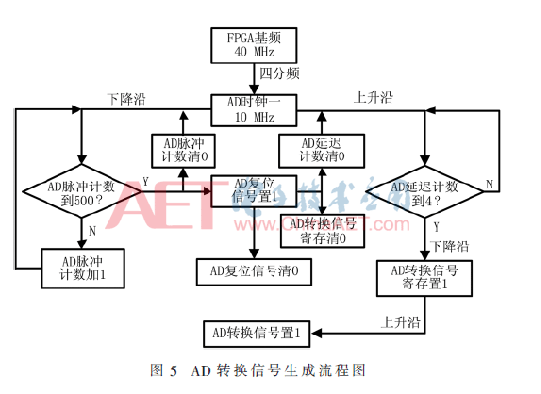

基于芯片 AD7606 采样转换时序的 AD 采样控制主要包括 AD 同步信号生成、AD 复位信号生成、AD 转换信号生成、AD 转换完成信号输出、AD 信号读取等流程。图 5 所示为以 FPGA 主频 40 MHz、10 kHz 采样频率为例的 AD 转换信号生成流程图。

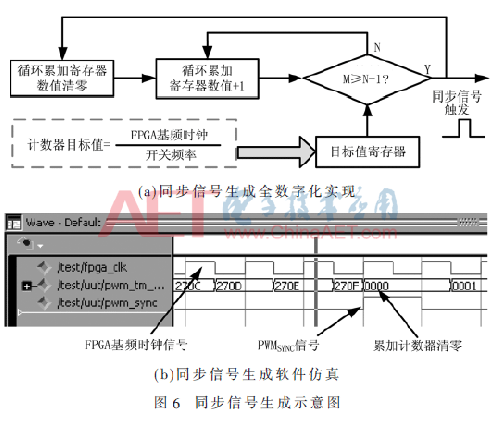

PWM 信号输出数字化实现方法为:利用计数器累加完成同步信号 PWMSNYC 的发生,同步信号的频率为电力电子设备的开关频率。同步信号的数字化生成及其软件仿真结果如图 6 所示。

3.3 CPLD 软件设计

CPLD 软件主要是对 FPGA 生成的 PWM 信号进行高速检测,并在故障时进行闭锁。具体实现方法为:FPGA 在产生 PWM 信号输出时,同时作为 CPLD 的输入信号,CPLD 程序对输入信号进行高速逻辑判断:若判断输入信号正常,则输出使能信号,完成 PWM 信号向开关器件的输出;否则输出闭锁信号,闭锁 PWM 信号输出,并向 DSP 和 FPGA 输出告警信号。

4 实验验证与结果分析

为验证本设计的可行性,在大型矿车制动能量回收与利用装置(以下简称“该装置”)上运用了本控制器。

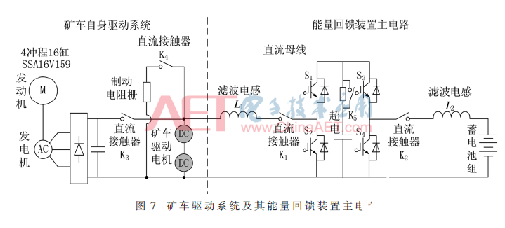

该装置是利用双向 Boost-Buck 变换电路结合超级电容和蓄电池实现矿车制动能量的回收的节能装置。图 7 所示为矿车驱动系统与该装置主电路拓扑结构图。

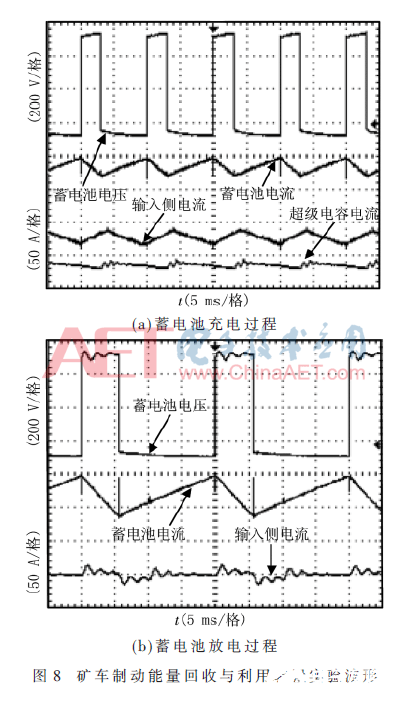

该装置直流母线电容为超级电容组,从左向右,当该装置吸收制动电流时,滤波电感 L1、开关器件 S1 和 S2 构成 Boost 升压电路,开关器件 S3 和 S4、滤波电感 L2 构成 Buck 降压电路;从右向左,当该装置释放蓄电池电能时,滤波电感 L2、开关器件 S3 和 S4 构成 Boost 升压电路,开关器件 S1 和 S2、滤波电感 L1 构成 Buck 降压电路。控制开关器件 S1、S2、S3 和 S4 的通断即可实现对矿车制动能量的回收与利用。在车载实验中,对该装置进行了若干功能性实验和保护动作实验。图 8 所示为部分实验波形,图 8(a)为蓄电池充电实验,此时直流母线电压为 1 500 V,充电电流为 20 A;图 8(b)为蓄电池放电实验,此时直流母线电压为 1 500 V,放电电流为 50 A。

用装置实现对矿车制动能量的回收与再利用。

5 结论

本文针对传统 DSP 控制系统在大功率电力电子设备应用中的不足,结合 DSP、FPGA、CPLD 三类主流控制芯片各自的特点,提出了一种适用于高压大功率电力电子设备的 DSP+FPGA+CPLD 的通用型控制器设计方案,并通过实际装置实验验证了本设计的可行性。其主要特点和优势如下:

(1)分析了大功率电力电子设备的控制需求,设计了主控制板与其他插件板相分离的硬件系统,方便应对不同控制对象时的插件板扩展;

(2)基于多时间尺度控保融合的软件设计理念,分别根据系统级、器件级和信号级的时间尺度提出了 DSP、FPGA 和 CPLD 软件设计流程;

(3)在大型矿车制动能量回收与利用装置上应用了本设计,实验波形证明本控制器设计的可行性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)