在上一篇文章中,我对计算机虚拟化的基本概念及MIPS架构如何有效地实现硬件虚拟化进行了阐述。本文将主要探讨多线程,并尝试对其内涵及用途进行定义。

线程是一序列的指令。多线程是指给定处理器(如CPU、GPU等)能运行多个线程。至于是什么构成了线程或子例程则没有过多界定,通常将线程看作任务或工作。

一个程序可以生成一个或多个线程。在当下的计算情境中,线程会争夺硬件资源。但如果是资源受限的环境则当如何呢?如果多核处理器运行了两个线程,则第一反应将是在每个内核上对线程进行平均分配。

但这似乎是一个“蛮力”的方法。是否有更佳的方式?答案是肯定的。这里就得提另一个问题了:多核处理器是否也是硬件多线程?

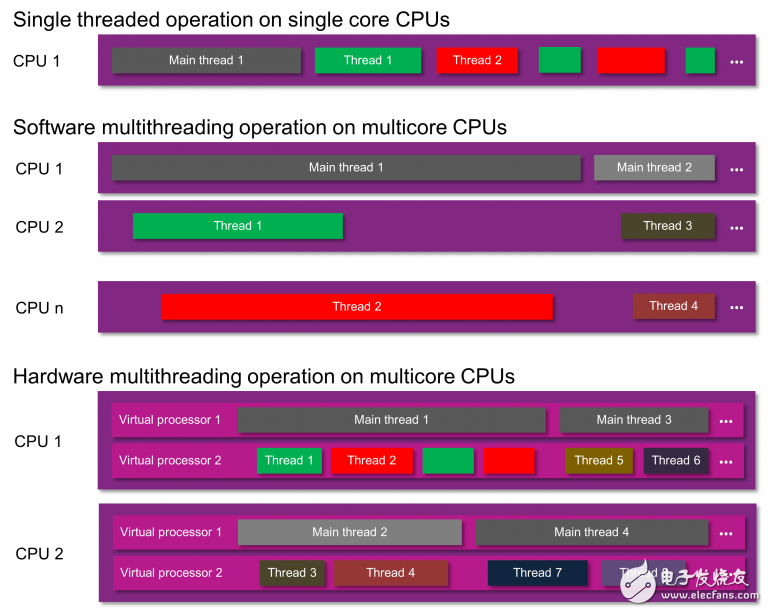

用于支持多线程的硬件技术通常与多核处理器上用于多任务计算机程序的软件机制相混淆。但二者有一个很明显的区别。下图阐述了硬件多线程和软件多线程之间的差别:

硬件多线程大幅度提升了管线的效率

从这里开始,对于MIPS架构通过MT扩展(MT ASE)和MIPS MT模块支持的硬件多线程,都使用术语“多线程”来表示。

嵌入式处理器强调性能。在过去的十年中,SoC设计师们越来越青睐多核来保证性能的可延展性。这场拉力赛将指引我们何去何从?主流的智能手机处理器已经从2012年时的1 GHz双核配置发展为2015年时的2.5GHz十核配置——相当于三年时间内CPU数量增长5倍。同时在这段时间里,处理技术也不断完善,处理器规格大幅减小,已从2012年的40 nm 变成如今的28 nm或14 nm。不过,似乎28 nm是主流处理器的主打规格,而16 nm或更小尺寸则主要用于高端计算市场。

这意味着CPU设计师需要找到其他解决方案来提高性能,同时又保持总体规格不断缩小。

内核数量自动翻倍意味着面积也翻倍,但性能却不一定也随之翻倍。事实上,基准测试数据表明,相比四核或八核CPU,双核CPU反而可以获得更佳的性能。

进一步提高CPU集群的频率是一种选择,但随之而来的是功耗管理。微架构改进(如绑定加载/存储指令、无序执行等)将带来实实在在的优势,但高端设计也可能会限制嵌入式市场应用程序的发展。同时还有执行效率的问题:一个单线程的CPU在闲置状态时可能会花大量时间等待内存中的数据。

多线程却巧妙地解决了上述问题。例如,选择双线程单核CPU可以即时提高30%~50%的性能,并且面积增加量非常微小。此外,激活线程是一个即时的过程,不需要消耗额外的功率(按逻辑讲,多核系统通常需要进行额外功率管理)。

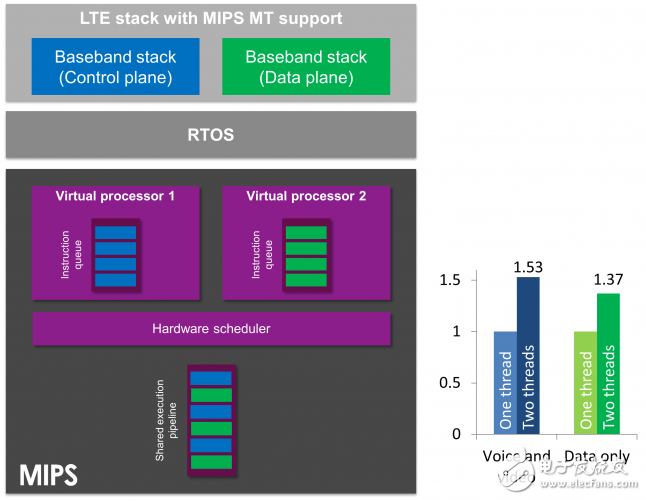

MIPS多线程使LTE应用程序的性能提高了50%

多线程适用于嵌入式SoC的另一个理由是:可靠的实时 *** 作。系统架构师可以动态地将线程分配至有需求的I / O服务中。例如,线程尝试从I / O系统读取数值、进入闲置状态,并于数据准备就绪时再进行激活。这样就减少了服务中断引起的开销。

使用多线程另一个重要的原因是,在缓存缺失及出现其他可能使线程停止的事件时,为每个CPU周期充分利用执行管道资源。

最后,多线程旨在为并行应用程序如网页浏览等提供强大的整体吞吐量。

总结以上信息得出的最直接的结论是,多线程适用于各种场景中。但MIPS CPU如何实现多线程?

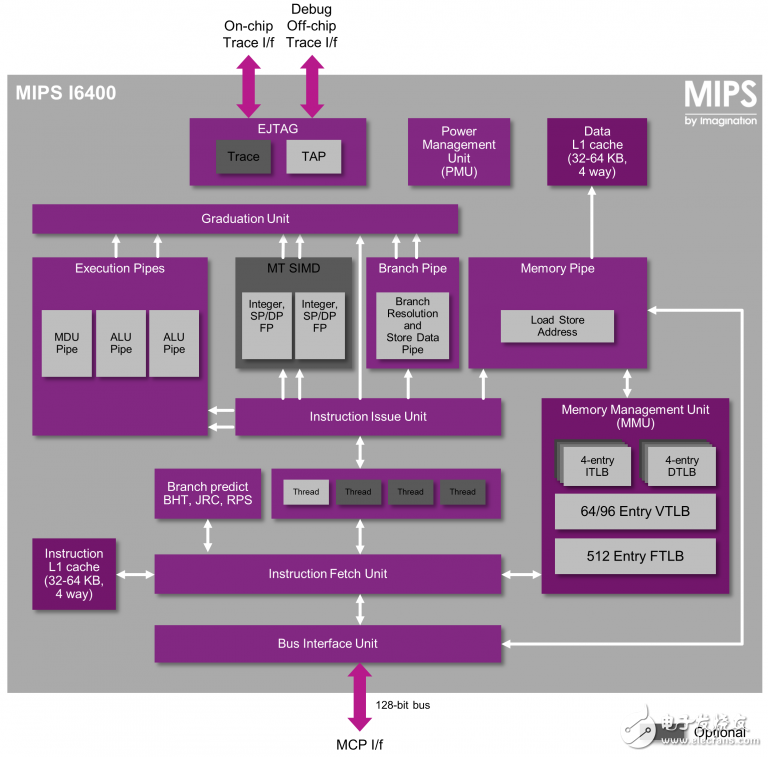

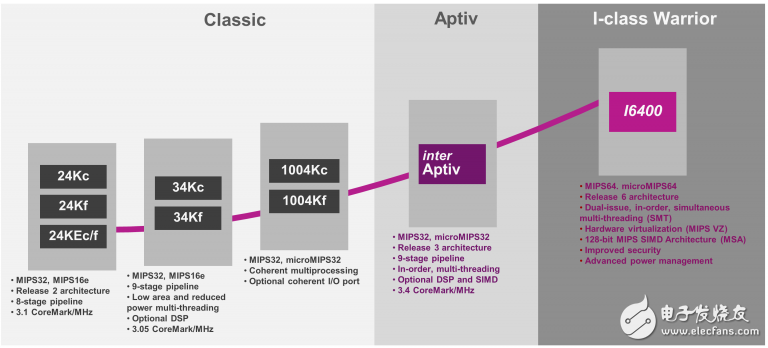

MIPS I6400是ImaginaTIon最新发布的实现了硬件多线程的CPU

可以通过现代 *** 作系统的速成课来了解多线程。当线程没有运行时,程序计数器(PC)需要存储线程接下来启动时的地址。此外,CPU必须跟踪所有程序员可见的寄存器中保存的值;而对于在用户模式下在MIPS CPU上运行的程序,则意味着必须跟踪通用寄存器(GPR)和乘法累加器 (MAC)。CPU为每个运行的线程存储了一个标识符,以及指示内核权限的标志(如:执行系统调用)。

在维护多个地址空间的多线程MIPS CPU上运行的 *** 作系统需要地址空间标示符(ASID)值,因为在翻译地址时硬件需要使用。

因此, MIPS CPU内的每个线程将包含一个PC和GPR副本,一个独特的线程ID,内核模式及ASID值。这些值构成了线程的内容。

MIPS CPU一直支持硬件多线程

目前比较通用的 *** 作系统可以检测和使用多线程硬件,包括SMP Linux、Android或Windows。ImaginaTIon与其生态系统伙伴密切合作,确保所有支持MIPS的 *** 作系统可以充分利用硬件多线程技术。例如,Express Logic的ThreadX在用于I级CPU的MIPS MT扩展顶端优化了上下文切换。

所以,不管是运行SMP基于Linux的分布如Android或实时 *** 作系统如ThreadX,如果其支持MIPS便可以支持多线程。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)