很多人问我FPGA的电源怎么怎么着,当然也有人瞎忽悠乱设计,当然我的设计也不是很完美。。。这里把我当年第一次设计FPGA,到现在的电源方案,几个演变、分析的过程,给大家讲讲。。。

(1)FPGA电源方案

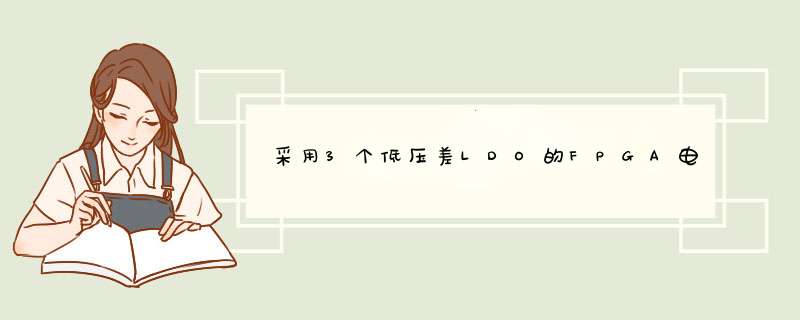

最后我们采用3.3V与1.2V的LDO,由于考虑到板卡3.3V逻辑,因此3.3V耗电量更大。因此选用了电流较大的LM1085,将5V转换为3.3V;接着使用1A的1117-1.2,再将3.3V转换为1.2V。。这样对于EP2C8Q208C8N而言,简单的电路实现3.3V与1.2V电源的供电,屡试不爽,轻松愉快。

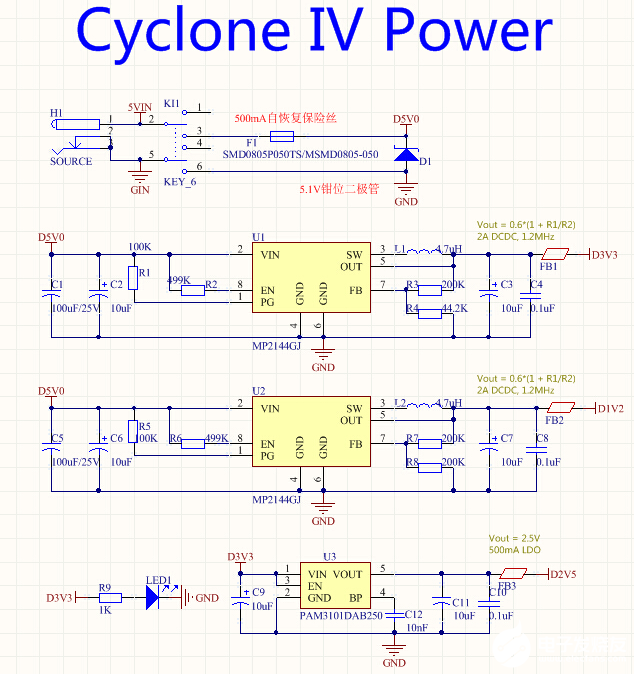

此外,这里的D1采用了5.1V的钳位二极管,防止短接、防止外部输入电压过高而烧坏电路!

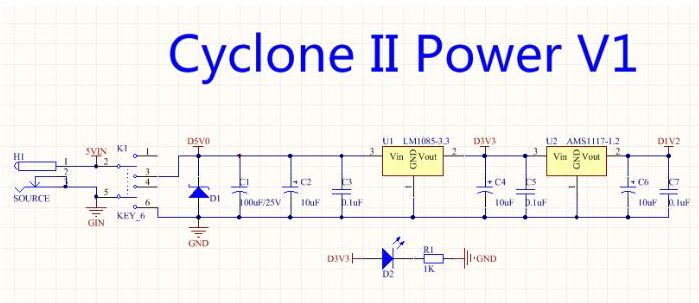

(2)随着对FPGA知识的增长,渐渐意识到原来的设计好像有问题。。FPGA非同与CPLD,内核功耗大于IO功耗,因此(1)中的设计,3.3V的LDO压力会很大,这倒是1085发烫,同时是1.2V不能很好的发挥。。因此后来我的电路,采用2路LDO并行分立设计,得到并行的3.3V与1.2V电压。采用了ADJ的LDO,同款LM1084-ADJ搞定,如下图所示:

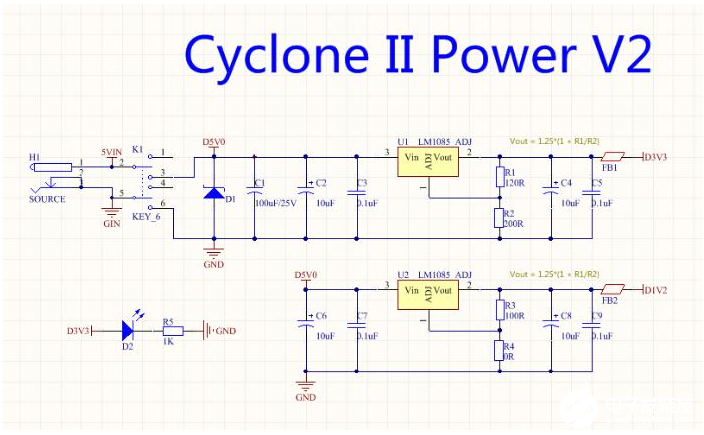

(3)随后又开始苛刻的追求,不仅仅追求代码、电路的极致,也追求板卡尺寸,体积的极限。实在没法忍受2个LM1084-ADJ那么庞大的体积,以及发热量、以及价格。于是转手准备使用DCDC来设计。这里我采用了1块多的MP2214,2路并行DCDC实现3A的3.3V与1.2V电压。这样电路将变得很温柔,丝毫没有发热,此外大大的降低了体积,一如既往。。。

(4)于是乎,从Cyclone III、Cyclone IV FPGA开始,还需要额外的2.5V的驱动电压,这里我采用了5毛钱的PAM3101DAB-250低压差LDO,最大300mA,已经完全够FPGA使用。

此外,在前面的基础上,又添加了自恢复保险丝,以防万一,防止电路烧坏,自恢复保险丝给我们带来了极大的乐趣……关于保险丝该在D1前面还是后面,官哥无意间看到我的电路,指点后认为将保险丝放在电路的最前端可靠,也就是目前的设计,如下:

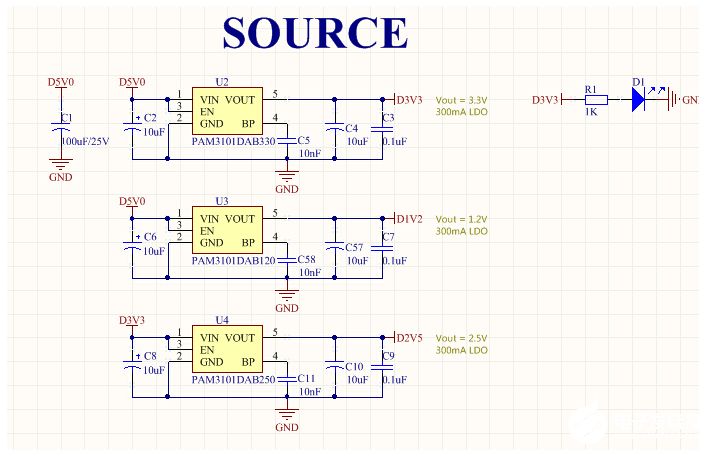

(5)不过还是不满足现状,2个DCDC还是挺大的。。。价格也较高。。在电流需求较小的地方,索性采用3个低压差LDO来完成电路的设计。。。我设计的工业相机用多个就是3个PAM3101DABXXX,如下所示。电路使用与比赛的呵呵,。,不过长时间测试,。,也很OK ,,木有问题,。,

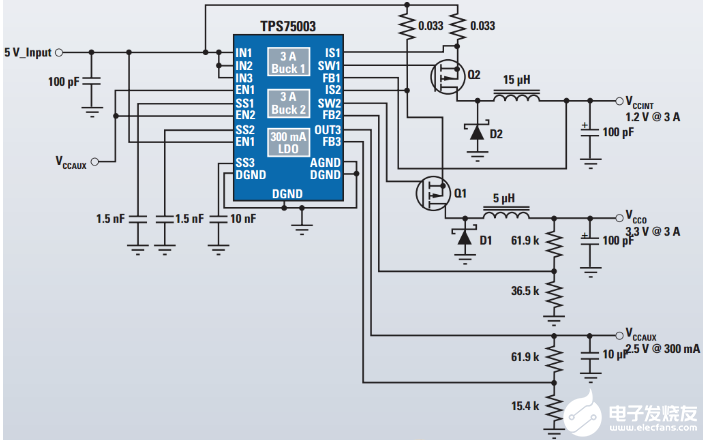

(6)3路并行电源,还是太臃肿有木有!!完美是没有极限的,我依然需要改变。比如TI退出的FPGA电源管理芯片TPS75003,能同时输出3A的3.3V、1.2V电压,以及2.5V 300mA的电压,。。。。可是价格有点贵,。。。。原理图如下:

不过豁出去了,下次用75003试试看!!

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)