1、概述

TDC-GP1主要应用于超声波流量仪、高能物理和核物理、各种手持/机载或固定工的高精度激光测距仪、激光雷达、激光扫描仪、CDMA无线蜂窝系统无线定位、超声波密度仪、超声波厚度仪、涡轮增压器的转速测试仪、张力计、磁致伸缩传感器、飞行时间谱仪、天文的时间间隔观测、频率和相位信号分析等高精度测试领域。TDC-GP1还提供了与微处理器的多种接口方式,用户可以很方便地用它构成自己的系统或仪器。

2、结构原理与引脚功能

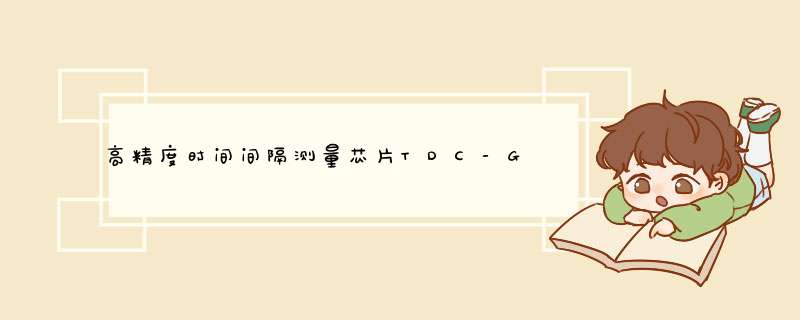

TDC-GP1采用44引脚TQFP封装,具有TDC测量单元、16位算术逻辑单元、RLC测量单元及与8位处理器的接口单元4个主要功能模块。内部结构如图1所示。

(1)TDC测量单元

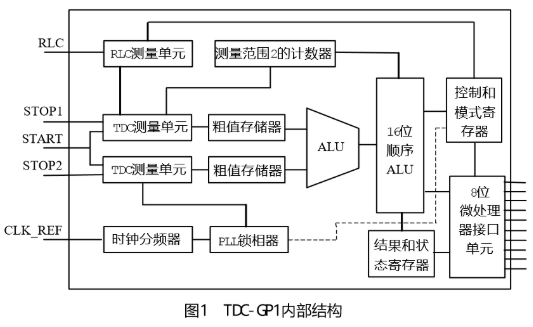

当两个脉冲的上升测或下降测的时间差为几十到几百ns时,传统的测量脉冲宽度的脉冲计数法已不再适用。这是因为要测的脉冲越窄,所需要的时钟频率就愈高,对芯片的性能要求也越高。例如要求1ns的测量误差时,时钟频率就需要提高到1GHz,此时一般计数器芯片很难正常工作,同时也会带来电路板的布线、材料选择、加工等诸多问题。为克服上述问题,TDC-GP1利用信号通过逻辑门电路的绝对传输时间提出了一种新的时间间隔测量方法,测量原理如图2所示。START信号和STOP信号之间的时间间隔由非门的个数来决定,而非门的传输时间可以由集成电路工艺精确地确定。同时,由于门电路的传输时间受温度和电源电压的影响比较大,因而该芯片内部设计了锁相和标定电路。

(2)16位算术逻辑单元

如图1所示,TDC-GP1有两个算术逻辑单元(ALU)。前面的ALU将粗值寄存器中的测量结果转变为一无符号整数,以便后面的ALU进行算术运算。后面的16位顺序ALU主要完成以下三方面的工作:按照控制寄存器中的指令进行时间间隔的计算;将计算出的结果进行标定;将标定后的结果进行乘法运行。ALU拥有独立的时钟,完成所有上述工作仅需4μs。

(3)RLC测量单元

TDC-GP1利用本身的时间间隔测量功能在芯片上集成了一个RLC测量单元。首先一已知电容通过被测电阻放电,当电容器上的放电电压达到比较器的门限电压外,TDC-GP1记录下这一段放电时间。然后将被测电阻变换为一已知阻值的电阻,重复上述过程得到另外一段放电时间。根据这两段放电时间的比值与已知电阻的阻值就可计算出被测电阻的阻值。

(4)与微控制器的接口单元

TDC-GP1提供了与8位单片机的接口,包括8位数据总线,4位可对16个寄存器 *** 作的地址线以及读、写、片选等控制线。另外,为了简化接口设计,还提供了地址锁存线(ALE)。

3、功能描述

TDC-GP1提供了两个量程及精度可调整等三个模式可供用户选择,每个模式中的分辨率可以设置为高或低。下面简要介绍一下三个模式的测试过程和时序。

(1)量程1

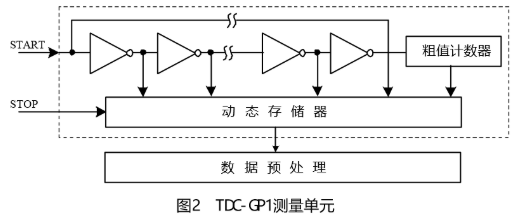

TDC-GP1提供了两个测量通道,每个通道精度250ps,两个通道精度等级完全相同;两个通道公用一个STSRT输入,可分别与四个独立的STOP输入进行比较,最小时限为15ns;START和STOP信号必须持续2.5ns以上,否则芯片无法辨识;STOP信号之间可进行相互的比较,无最小时限;量程为3ns~7.6μs;两个通道可进行排序,这样可使1通道允许8个脉冲输入,这种模式下通道2的STOP输入被忽略。图3给出了量程1的测量时序。

(2)量程2

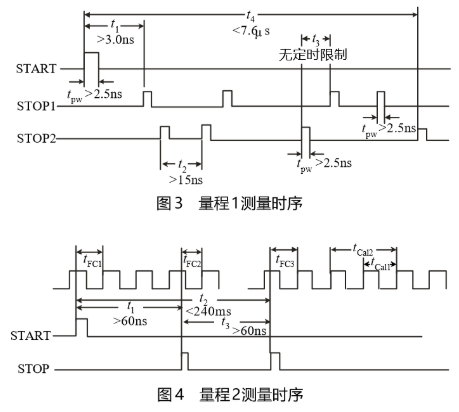

为进行大量程时间测量,芯片引入了一个16位的predivider。该模式下芯片只有通道1可用;正常精度模式下允许4个脉冲输入;STOP信号之间不能相互比较,仅STOP与STSRT信号可进行比较;最大量程60ns~200ms。图4给出了量程2的测量时序。

原理如下:输入START信号,芯片内部迅速测量出这个信号与下一个校准时钟上升测的时差,记为tFC1。之后,计数器开始工作,得到此predivider的工作周期数,记为period。这进,重新激活芯片内部测量单元,测量出输入的STOP信号的第一个脉冲上升沿与下一个校准时钟上升沿的时差,记为tFC2。TFC3是STOP信号的第二个脉冲上升沿与校准时钟上升沿的时差,tCall是一个校准时钟周期,tCal2是两个校准时钟周期。根据图4可以得出START信号与STOP信号第一个脉冲的时间间隔为

TIme=period×[cc+(tFC1-tPC2)/(tCal2-tCal1)

cc表示predivider的计数值。

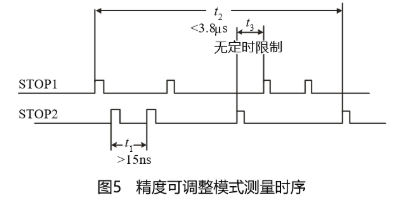

(3)精度可调整模式

TDC芯片另一个重要特征是器件引入了精度调整模式。在此模式下,两通道数值会非常精确。校准环路由外部时钟引入作为参考。我们可以通过对芯片内部寄存器的设置工作于此模式,因此,结果的精度取决于程序中的设置。精度可调整模式不需要START信号,因此最多只能通过通道1和通道2共引入8个STOP输入。此时,任意两个STOP信号均可以进行比较,量程为3ns~3.8μs。工作于精度可调整模式,芯片耗电量比较大,大约为25mA。图5给出了精度可调整模式的测试时序。

4、应用实例

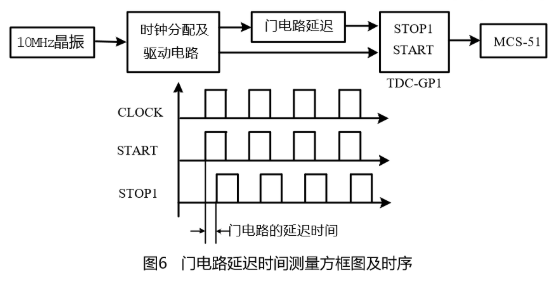

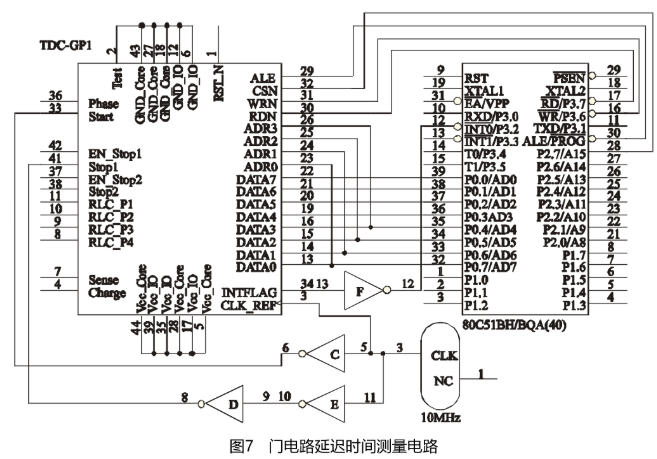

高速逻辑门电路的延迟时间一般只有几ns,用以前的脉冲计数法无法对之进行测量。使用TDC-GP1后,这类工作就变得相对容易多了。图6是它的测量方框图及时序图,图7是具体电路原理。应用量程1的寄存器设置为: Reg0:0x44;Reg1:0x4D;Reg2:0x01;Reg3:0xXX;Reg4:0xXX;Reg5:0xXX;Reg6:0x02;

Reg7:0x01;Reg8:0x00;Reg9:0x00;Reg10:0x80。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)