作者:?圆宵?FPGA那点事儿

在ISE时代,使用的是UCF约束文件。从Vivado开始,XDC成了唯一支持的约束标准。XDC除了遵循工业界的通行标准SDC(Synopsys Design Constraints)之外,还加入了XILINX FPGA特有的位置物理约束等特性。以下是在实际使用中,经历过一些经验教训后,体会的几点我们在组织XDC约束时需要注意的事项。

1. XDC约束条目是有先后顺序的

XDC里面每一行相当于一条指令,Vivado按照行序从前往后读取XDC指令,所以越后面的XDC指令,其优先级越高。比如当有2条XDC指令约束同一个东西时,后面指令会因为执行的比较晚,而覆盖前一条指令的效果,这点需要我们特别注意!

因为XDC中的指令有先后顺序,所以推荐的XDC文件组织方式一般是把TIming约束放在前面,而把物理位置约束放在后面。如果更具体些,可以遵循下面的顺序:

## TIming AsserTIons SecTIon

# Primary clocks

# Virtual clocks

# Generated clocks

# Clock Groups

# Input and output delay constraints

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

## Physical Constraints Section

2. 一个Vivado工程中可以添加多个XDC文件

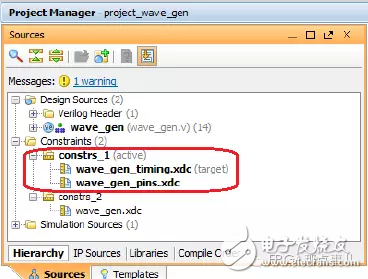

这样的好处是便于管理组织。因为XDC约束条目是有顺序要求的,所以XDC文件也是有先后顺序的,我们可以在GUI界面通过鼠标拖拽,来调整XDC文件的顺序。一般推荐把Timing约束,同物理位置属性约束,分别放到不同的文件当中,就如同下面所做的那样:

另外请注意,VIVADO不但可以支持多个XDC文件,还可以支持多组XDC文件集合,但是同时只能有1个集合起作用。如果我们一次create多个synthesis或者implementation,我们还可以为它们每一个分别制定使用哪个约束文件。这个特性在时序收敛阶段比较有用。

3. 关于XDC文件的指令和注释

在XDC里面,每个完整的XDC约束指令不应当跨行,必须在一行之内表达完毕。同样,在一行之内也只允许存在一个约束指令,不可以把2个约束放在同一行。

关于注释(以“#”开头),唯一的一点限制是,在有效的XDC约束指令行末,不可以添加“#”开头的注释,否则Vivado工具会理解错误。这跟我们在其它语言中通常所理解的注释语法不太一样,可能需要建议XILINX改进。

错误:

正确:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)