硬件平台:ZedBoard

软件平台:vivado2013.3

本示例通过综合、实现,生成比特流,发送到SDK实现。

启动vivado并且创建一个项目

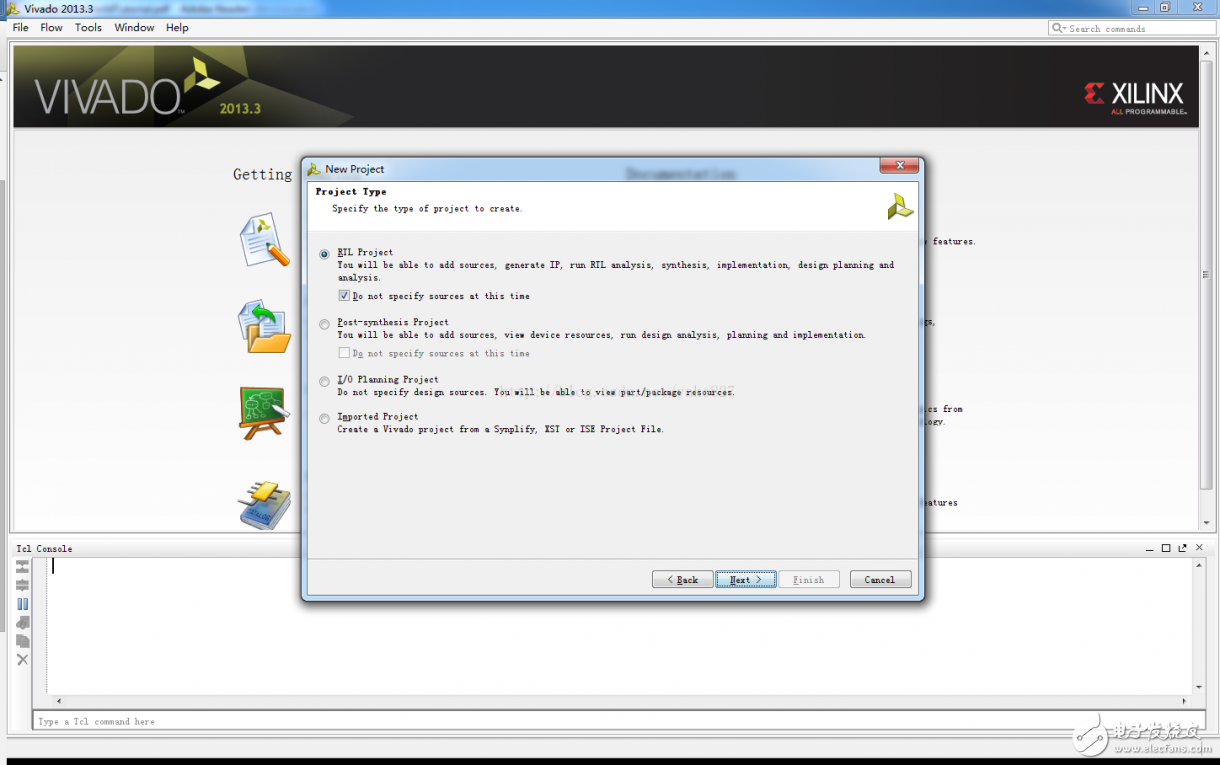

根据提示 *** 作一步步创建新项目的时候记得选择RTL Project

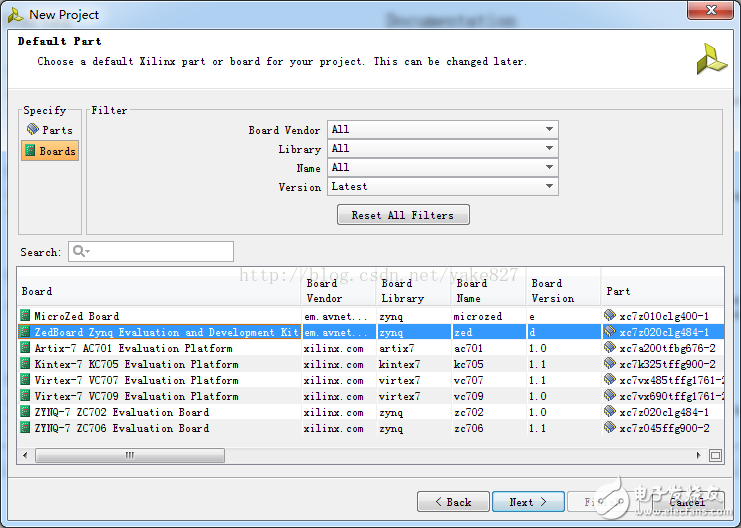

板子选择ZedBoard,其他默认。

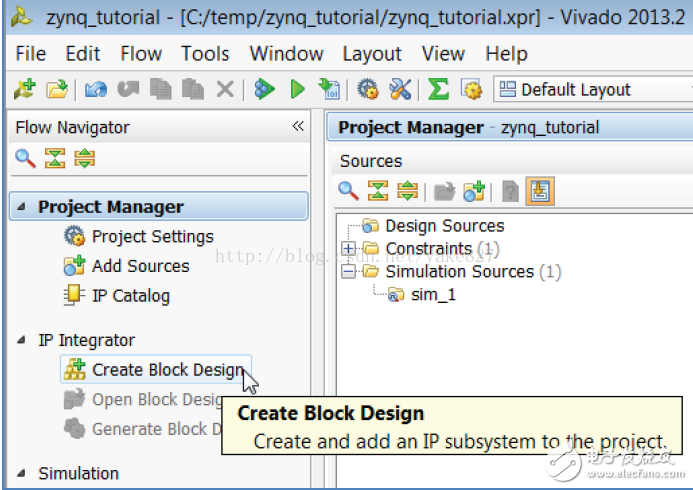

创建一个IP综合设计

在IP Integrator中选择Create Block Design

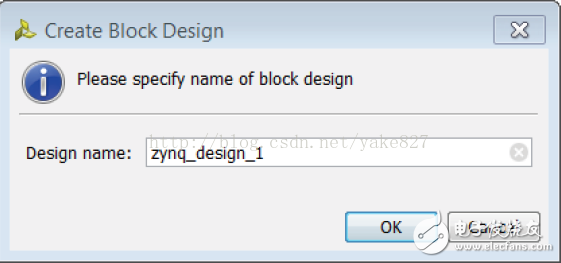

在Create Block Designd出页,为IP子系统设计定义个名字

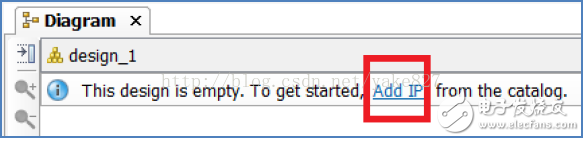

在IP子系统中,在中间的Diagram中选择Add IP

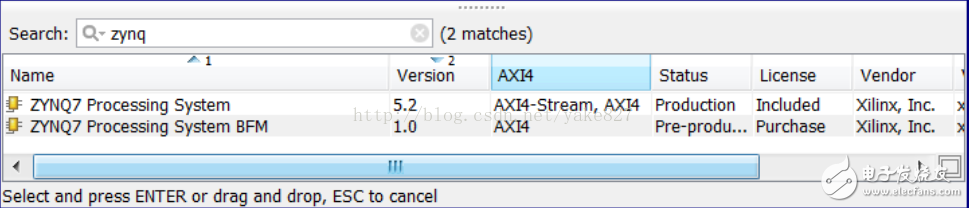

在搜索页,输入zynq找到ZYNQ7 Processing System IP

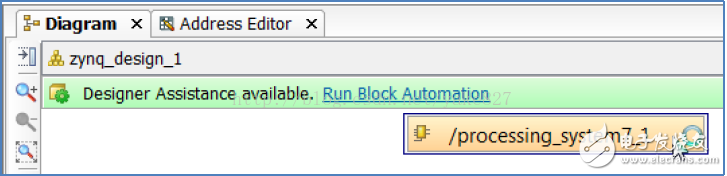

在Diagram页,点击Run Block AutomaTIon,然后Run Block AutomaTIon对话框打开,选择/processing_system7_1,这时,会出现一个对话框,这个IP核会自动为FIXED_IO和DDR接口创建外部连接,点击OK。

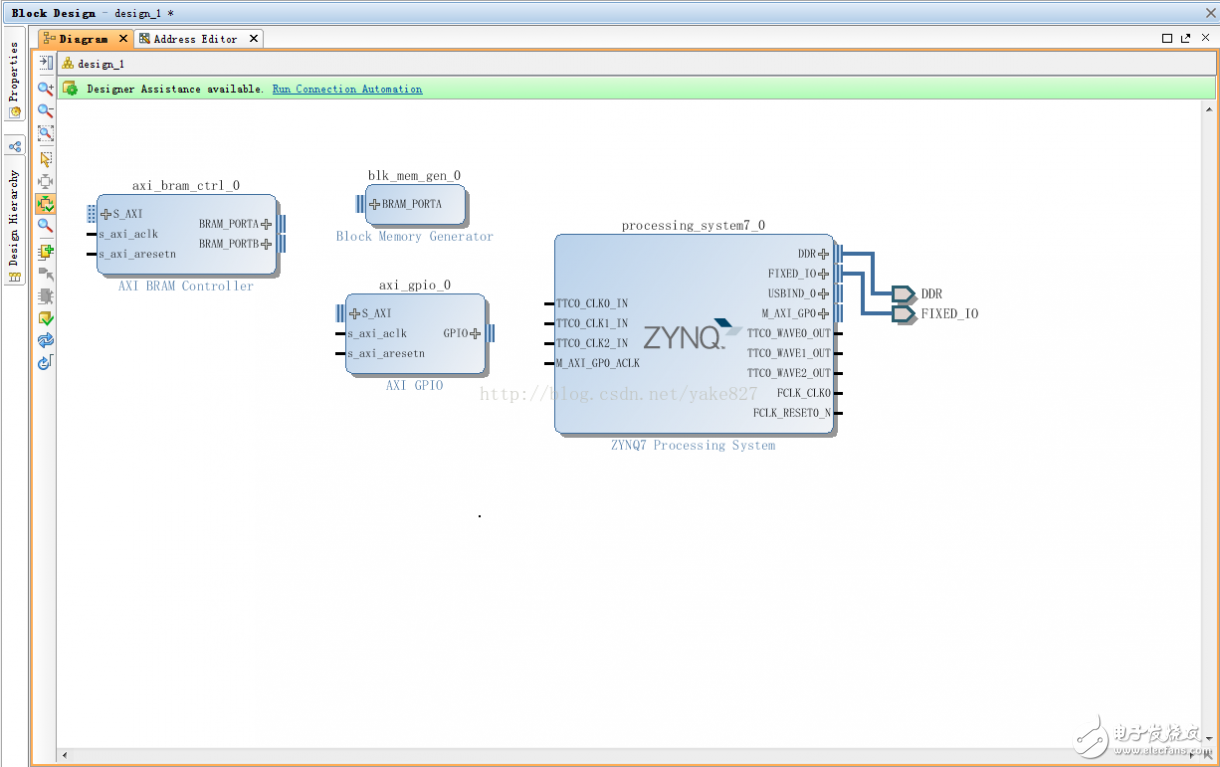

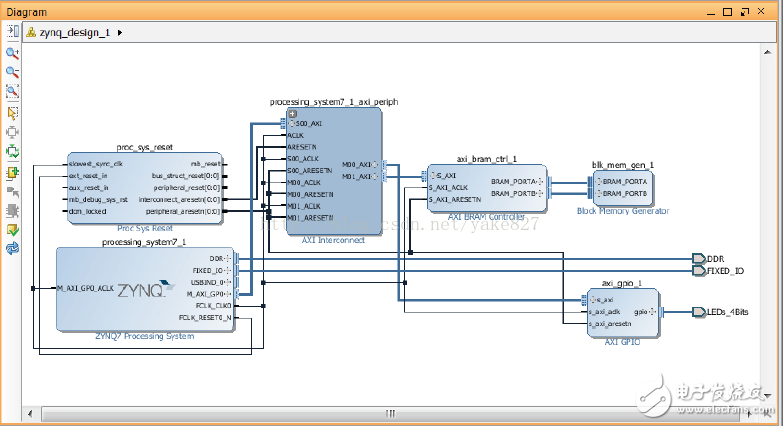

用同样的方法,我们增加外设,在Diagram右击,选择Add IP,在搜索页,输入gpio找到AXI GPIO IP,点击enter确认添加,重复上述步骤,输入axi bram添加AXI BRAM Controller;输入block加入Block Memory Generator。完成之后的窗口如下所示:

根据要求定制IP核

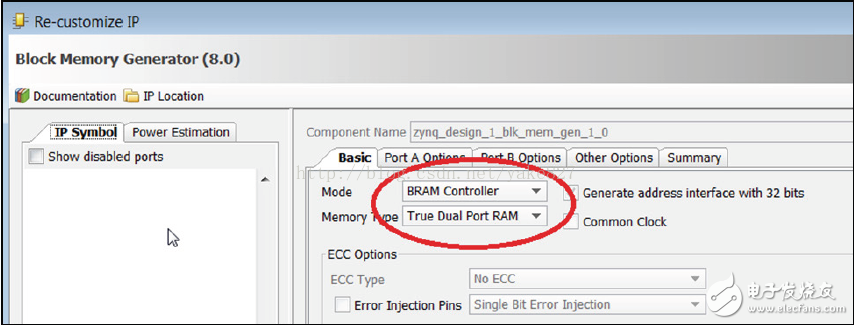

双击Block Memory Generator进入Re-?-customize IP界面,在Basic页,将Mode设置为BRAM Controller,Memory Type设置为True Dual Port RAM。其中AXI BRAM Controller为Block Memory Generator提供AXI内存映射接口。

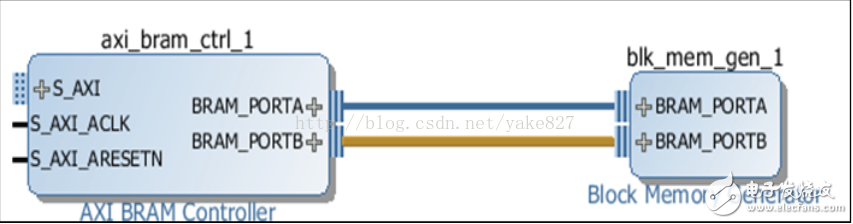

通过点击连接点并拖动连线将Block Memory Generator与AXI BRAM Controller连接起来

使用Designer Assistance

Block Designer Assistance可以帮助我们将AXI GPIO和AXI BRAM Controller连接到Zynq-7000 PS。

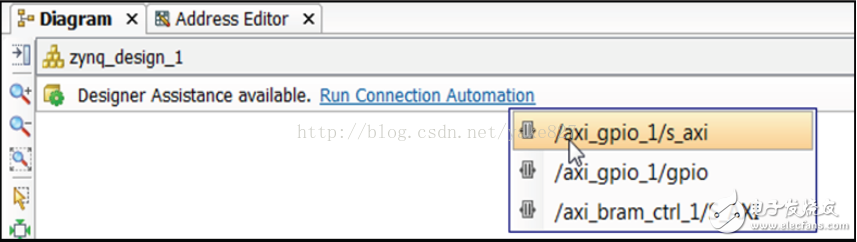

1.点击Run ConnecTIon AutomaTIon然后选择/axi_gpio_1/s_axi将GPIO IP和BRAM Controller连接到Zynq PS上

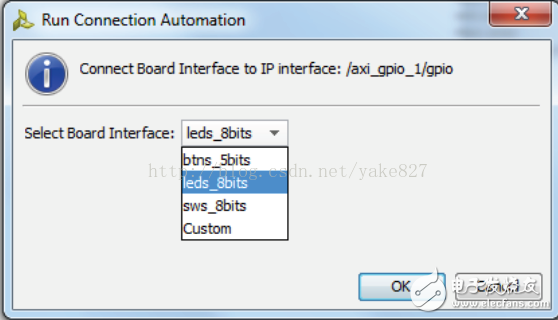

2.再次选择Run Connection Automation,连接/axi_gpio_1/gpio,然后会d出一个对话框,选择板子接口为leds_8bits。这一步可是配置IP核,创建一些必要的文件约束(XDC)

3.再次再次选择Run Connection Automation,选择剩下的/axi_bram_ctrl_1/S_AXI选项,这样就完成了Zynq7 PS与AXI BRAM Controller的连接。布局完成的连线如下所示:

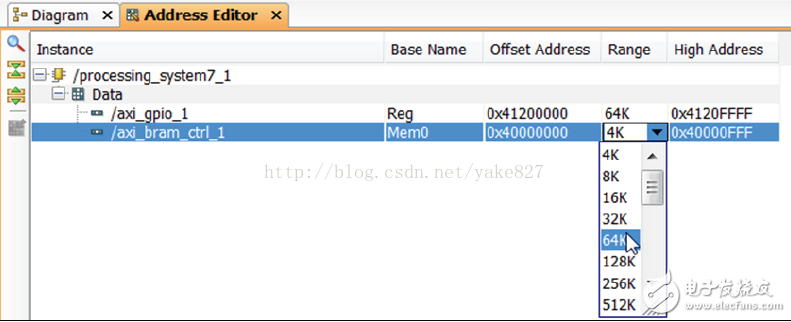

打开Address Editor标签页,这里是我们所使用的IP的内存映射,在这里有两个IP:GPIO和BRAM Controller,一般来说Vivado会自动分配这些内存映射,我们也可以修改它,这里把AXI BRAM Controller改成64K。

保存配置(CTRL+S);

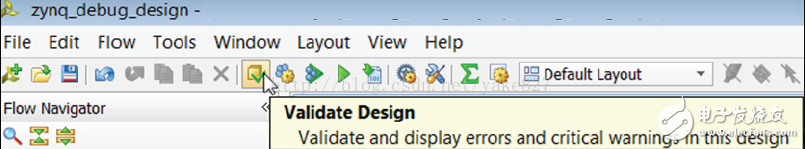

在工具栏那里,通过Validate Design按钮运行DRC(Design-Rules-Check)

如果成功会d出成功的对话框。

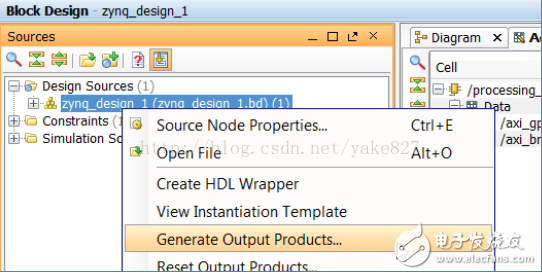

生成HDL设计文件

在Sources窗口,右击顶层子系统设计选择Generate Output Products,这会生成用于结构图IP核的源文件和相关的约束文件。

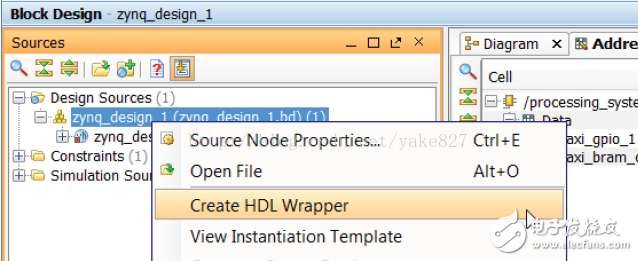

还是在顶层子系统设计选择Create HDL Wrapper创建一个顶层HDL文件

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)