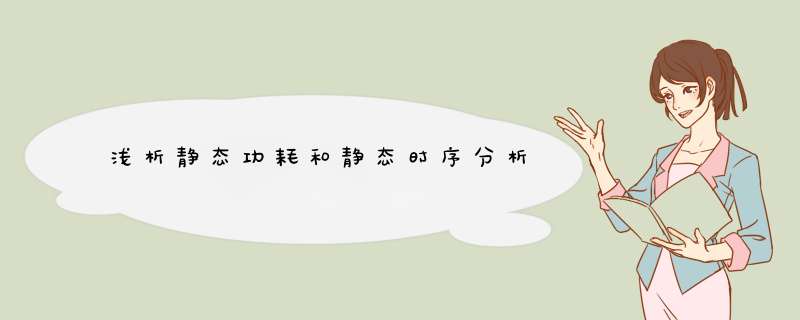

静态时序分析

STA贯穿设计过程的各个阶段,从RTL逻辑综合到布局、时钟树综合、布线和反标,直到tape_out。每一次分析的目的都是为了检查当前设计的结果是否满足设计的约束条件。

在做时序分析时,总延迟的期间延迟部分由时序库提供,互连线延迟部分在每一阶段是不一样的。前者在设计中随后者的变化而变化。即随着RC对器件负载和信号转换在不断的更新和变化。

功耗分析

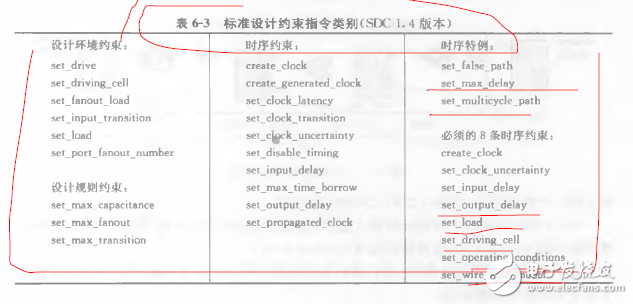

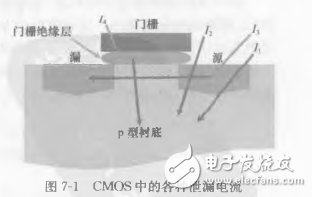

静态功耗分析

静态功耗又称泄漏功耗,它是指电路处于等待或不激活状态时泄露电流所产生的功耗。泄露电流主要有4种:

动态功耗

指芯片工作中,晶体管处于跳变状态所产生的功耗,主要由动态开关电流引起的动态开关功耗以及短路电流产生的短路功耗两部分组成。

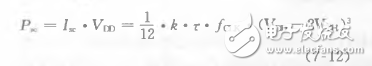

开关功耗

短路功耗

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)