光耦似乎能在不同地电势工作的电路之间实现简单的直流隔离,但这只是表面现象。光耦会从被隔离电路上吸取电能,转换相对缓慢,并且具有LED老化的不确定性。现在有一些不用光耦的替代品,如Analog Devices公司的ADUM12xx或德州仪器公司的ISO72x。本设计实例将描述一种光耦的简单改进方法。

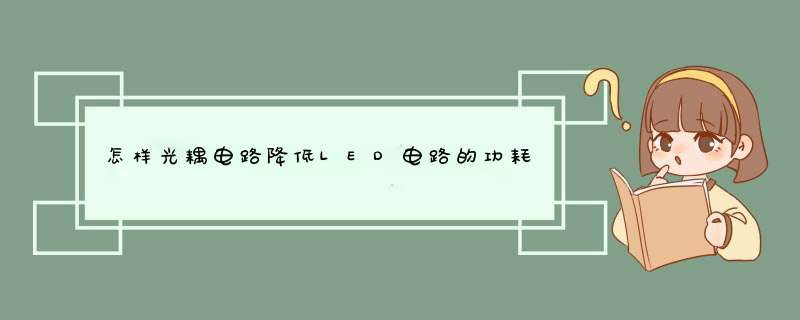

图1是两个常见的0 V交流同步设计。它试图通过相应增加光耦的负载电阻值,以降低光耦的LED电流,从而减少隔离电路的功耗,但结果是较慢和更不确定的开关速度。为实现较快而干脆的开关,就必须牺牲电源效率;不过,这种牺牲获得的优点也是有限的,因为电源效率与交流电压强度呈反向关系。

如光耦在几乎所有AC周期中均连续发光超过标称值,会导致低的电源效率,以及光耦相对快速的老化。一个更大的缺点是过大并且几乎无法控制的过零失真,因为电路的灵敏度阈值依赖于光耦的参数。图1中的设计并未提供一种理想的方案。至于效率,根据光耦的电流传输比与AC波幅,它们吸入的电流为5mA~100mA。

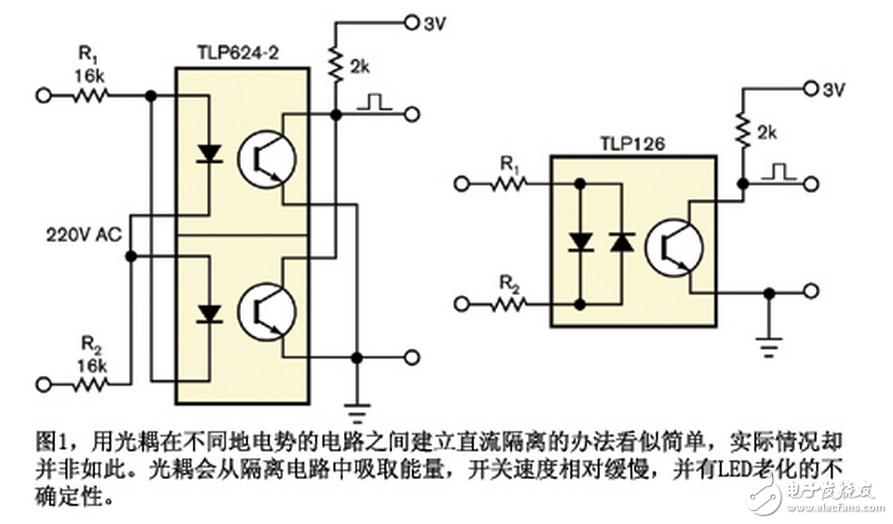

图2中的设计解决了过高功耗、不确定开关与LED老化的问题,因此非常适合于宽AC范围的应用。与图1中的电路相比,图2的LE

D只在接近于零交越点时才发光,并从以前充电的电容中获得能量,因此能将平均电流降低十分之一至百分之一。该设计亦提供更快、更确定和更陡的转换。此外,也减缓了可预期的LED老化问题。图1中的电阻R1与R2的热耗不到1.5 W,因此将它们更换为0.1 W器件可以在相同电路板面积上放置更多元件(图2)。

电路的主要元器件包括波幅探测器D1、电容C1和施密特触发器Q1/Q2,用于控制通过光耦LED的电流。D2和D3用于稳定Q2的基极电压,同时也稳定了启动光耦的集电极电流。电容C1通过R1、R2和D1充电。

在几乎所有交流周期内,除接近零交越点以外,Q1都是on,而Q2为off。因此,接近零交越点时,施密特触发器Q1与Q2的状态翻转,Q2使电容C1恒流放电,因为由Q2、D2、D3、R5和R6构成的电路将电流稳定在I = (2 × VD - VBE2) / R6,其中VD是在D2或D3上的压降,而VBE2为Q2的基射电压。

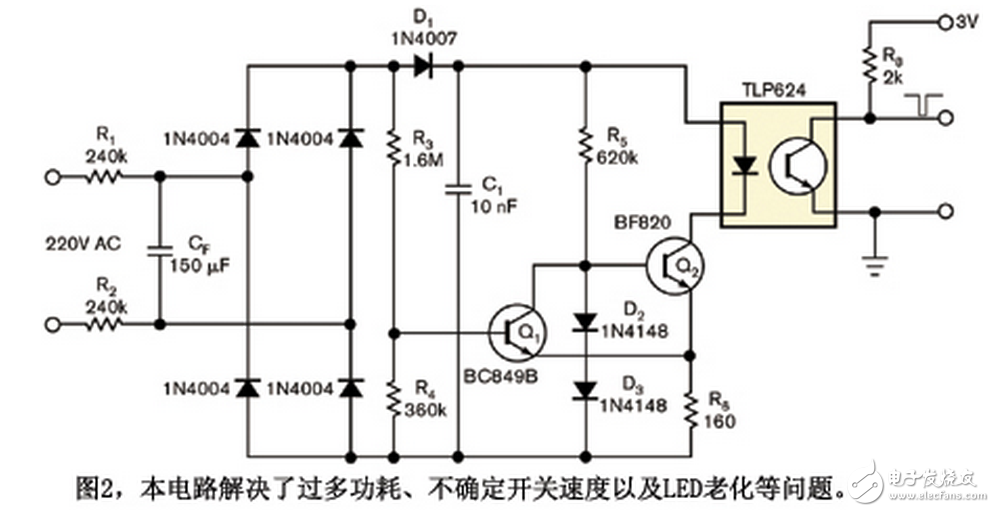

施密特触发器有天生的迟滞效应,而有些应用不需要这种迟滞,图3就是这样一种设计。它亦表示了在不要求D1最小反向电流时的方法。但这个电路最适用于纯同步和非可控硅控制。由于LED电流的稳定性,这些设计扩展了交流输入电压范围,可能对多种交流供电的小产品很有用;并且是一个设定LED电流,又没有LED过载的风险;并且也减少了对光耦稳定性的影响。这些设计的一个更大的优点是,它们自身就具有更安全的特性。如遇端子短路情况,隔离与非隔离两侧之间的电流比图1电路能小十分之一至百分之一。光耦亦有优点。由于低占空比,可以自由减少光耦负载电阻R8的值,而不会损失电源效率。这种减小可获得低的零交越错误。

未来LED封装形式将往那些方面发展?1、中功率成为主流封装方式。目前市场上的产品多为大功率LED产品或是小功率LED产品,它们虽各有优点,但也有着无法克服的缺陷。而结合两者优点的中功率LED产品应运而生,成为主流封装方式。

2、新材料在封装中的应用。由于耐高温、抗紫外以及低吸水率等更高更好的环境耐受性,热固型材料EMC、热塑性PCT、改性PPA以及类陶瓷塑料等材料将会被广泛应用。

3、芯片超电流密度应用。今后芯片超电流密度,将由350MA/mm2发展为700MA/mm2,甚至更高。而芯片需求电压将会更低,更平滑的VI曲线(发热量低),以及ESD与VF兼顾。

4、COB应用的普及。凭借低热阻、光型好、免焊接以及成本低廉等优势,COM应用在今后将会得到广泛普及。

5、更高光品质的需求。主要是针对室内照明,晶台光电将会以LED室内照明产品RA达到80为标准,以RA达到90为目标,尽量使照明产品的光色接近普兰克曲线,这样的光才能够均匀、无眩光。

6、国际国内标准进一步完善。相信随着LED封装技术的不断精进,国内国际上对于LED产品的质量标准也会不断完善。

7、集成封装式光引擎成为封装价值观。集成封装式光引擎将会成为晶台下一季研发重点。

8、去电源方案(高压LED)。今后室内照明将更关注品质,而在成本因素驱动下,去电源方案逐步会成为可接受的产品,而高压LED充分迎合了去电源方案,但其需要解决的是芯片可靠性需要加强。

9、适用于情景照明的多色LED光源。情景照明将是LED照明的核心竞争力,而未来LED照明的第二次起飞则需要依靠情景照明来实现。

10、光效需求相对降低,性价比成为封装厂制胜法宝。今后室内照明不会太关注光效,而会更注重光的品质。而随着封装技术提高,LED灯具成本降低成为替代传统照明源的动力,在进入家庭照明的过程中,性价比将会越来越被客户所看重。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)