在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型:

A. AXI4-Interface:支持Stream,Lite,Full共3中类型

B. NO I/O协议:无端口协议

C. Wire Handshakes:握手协议

D. Memory Interface:内存访问型的端口协议

接下来的几章,我们重点介绍下AXI接口类型如何在HLS中实现,首先看Lite端口:

AXI-Lite端口的实现

使用Vivado HLS的AXI-Lite端口,可以实现:

把多个port打包到一组AXI-Lite总线空间内

输出相应的驱动c driver

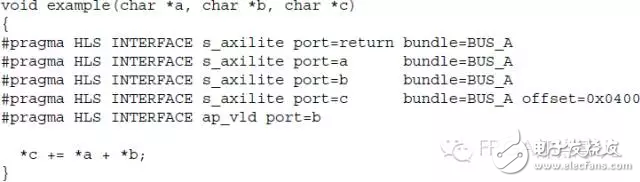

下面看一个例子:

#pragma HLSINTERFACE s_axilite port=a/b/c bundle=BUS_A

的意思是把端口a,b,和c都打包到axi-lite端口里面,总线的名字叫做BUS_A,它等效为s_axilite & ap_none

#pragma HLSINTERFACE s_axilite port=return bundle=BUS_A

的意思是把函数的控制端口,也即Block Level Interface也打包进AXI-Lite

#pragma HLS INTERFACE ap_vld port=b

的意思是b端口在axi寄存器 *** 作的时候,也需要遵循一定的协议。具体是b会有3个register与之相对应,一个register用来读数据,一个寄存器用来表明数据有效可读,一个register告诉master数据已经被读取,master可以写入下一个数据。

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A offset=0x0400

中offset的意思是端口C的地址在axi-lite端口中的地址偏移

有时候,还可以对c做如下约束:

#pragma HLS INTERFACE s_axilite port=c register bundle=BUS_A

register的意思是,c的输出会被寄存输出,并且输入会在模块启动的第一个clock cycle被读取,它等效为s_axilite & ap_ovld

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)