在之前的3章里,着重讲解了HLS对AXI端口(包括axi-lite,axi-stream和full axi端口)的综合实现问题,下面让我们来介绍一下其它的端口类型是如何实现的。

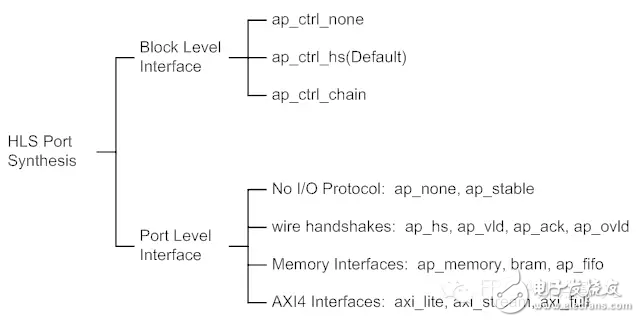

在开始之前,先来个总结回顾,看看HLS支持的端口类型分类:

下面详细介绍下BlockLevel Interface

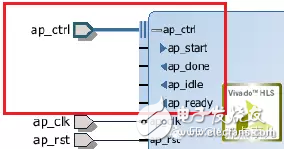

ap_ctrl_hs:

是默认的端口类型,它综合出来的端口会有额外的4个系统控制信号,如下所示:

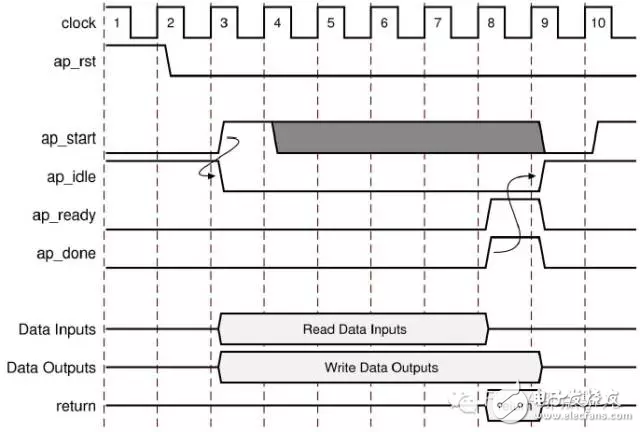

其端口行为时序如下:

在ap_rst释放后,ap_start高电平启动模块的运行,然后ap_idle立即拉低表明模块不再空闲。

ap_ready拉高表明本模块已经准备好接收新的输入,不过它的行为会稍微有些复杂,在non-pipelined实现中,ap_ready和ap_done会同时拉高;在pipelined实现中,它可能会随时拉高。

ap_ctrl_none

它同ap_ctrl_hs简化许多,没有上面的系统控制信号。

ap_ctrl_chain

它同ap_ctrl_hs几乎一样,除了多出一个输入信号ap_conTInue,它可以使得下游模块控制上游模块的运行/终止。不过这种模式比较不常用,所以有兴趣的读者,可以自己去研究相关的文档。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)